# F<sup>2</sup>MC-16LX FAMILY 16-BIT MICROCONTROLLER ALL 16LX SERIES

# HARDWARE SET UP

**APPLICATION NOTE**

# **Revision History**

| Date       | Issue                                   |

|------------|-----------------------------------------|

| 2003-08-18 | V1.0; First version; MWi                |

| 2004-01-16 | V1.1; Specification changed; MWi        |

| 2004-03-09 | V1.2; Pin connection chapter added; MWi |

| 2004-03-22 | V1.3; Corrections done                  |

This document contains 14 pages.

# Warranty and Disclaimer

To the maximum extent permitted by applicable law, Fujitsu Microelectronics Europe GmbH restricts its warranties and its liability for **all products delivered free of charge** (eg. software include or header files, application examples, target boards, evaluation boards, engineering samples of IC's etc.), its performance and any consequential damages, on the use of the Product in accordance with (i) the terms of the License Agreement and the Sale and Purchase Agreement under which agreements the Product has been delivered, (ii) the technical descriptions and (iii) all accompanying written materials. In addition, to the maximum extent permitted by applicable law, Fujitsu Microelectronics Europe GmbH disclaims all warranties and liabilities for the performance of the Product and any consequential damages in cases of unauthorised decompiling and/or reverse engineering and/or disassembling. **Note**, **all these products are intended and must only be used in an evaluation laboratory environment**.

- 1. Fujitsu Microelectronics Europe GmbH warrants that the Product will perform substantially in accordance with the accompanying written materials for a period of 90 days form the date of receipt by the customer. Concerning the hardware components of the Product, Fujitsu Microelectronics Europe GmbH warrants that the Product will be free from defects in material and workmanship under use and service as specified in the accompanying written materials for a duration of 1 year from the date of receipt by the customer.

- 2. Should a Product turn out to be defect, Fujitsu Microelectronics Europe GmbH's entire liability and the customer's exclusive remedy shall be, at Fujitsu Microelectronics Europe GmbH's sole discretion, either return of the purchase price and the license fee, or replacement of the Product or parts thereof, if the Product is returned to Fujitsu Microelectronics Europe GmbH in original packing and without further defects resulting from the customer's use or the transport. However, this warranty is excluded if the defect has resulted from an accident not attributable to Fujitsu Microelectronics Europe GmbH, or abuse or misapplication attributable to the customer or any other third party not relating to Fujitsu Microelectronics Europe GmbH.

- 3. To the maximum extent permitted by applicable law Fujitsu Microelectronics Europe GmbH disclaims all other warranties, whether expressed or implied, in particular, but not limited to, warranties of merchantability and fitness for a particular purpose for which the Product is not designated.

- 4. To the maximum extent permitted by applicable law, Fujitsu Microelectronics Europe GmbH's and its suppliers' liability is restricted to intention and gross negligence.

#### NO LIABILITY FOR CONSEQUENTIAL DAMAGES

To the maximum extent permitted by applicable law, in no event shall Fujitsu Microelectronics Europe GmbH and its suppliers be liable for any damages whatsoever (including but without limitation, consequential and/or indirect damages for personal injury, assets of substantial value, loss of profits, interruption of business operation, loss of information, or any other monetary or pecuniary loss) arising from the use of the Product.

Should one of the above stipulations be or become invalid and/or unenforceable, the remaining stipulations shall stay in full effect

# Contents

| R | EVISIO | ON HIST  | ГОRY                                       | 2  |

|---|--------|----------|--------------------------------------------|----|

| W | ARRA   | ANTY A   | ND DISCLAIMER                              | 3  |

| C | ONTE   | NTS      |                                            | 4  |

| 0 | INTR   | ODUCT    | TION                                       | 5  |

| 1 | MINI   | MAL SY   | ′STEM                                      | 6  |

|   | 1.1    | Schema   | atic                                       | 6  |

|   | 1.2    |          | nterface                                   |    |

|   | 1.3    | Powers   | supply                                     | 6  |

|   | 1.4    |          | Digital Converter Supply Pins              |    |

|   | 1.5    | _        | Input Pins                                 |    |

|   | 1.6    | Reset F  | Pin (RSTX)                                 | 7  |

|   | 1.7    | C Pin    |                                            | 7  |

|   | 1.8    | Clock S  | Source                                     | 7  |

|   | 1.9    | Mode F   | Pins                                       | 7  |

|   |        | 1.9.1    | Flash-Asynchronous-Serial-Programming-Mode | 7  |

|   |        | 1.9.2    | Free-Running-Mode                          | 8  |

|   | 1.10   | NC Pin   | s 8                                        |    |

| 2 | LAY    | OUT AN   | D ELECTROMAGNETIC COMPATIBILITY            | 9  |

|   | 2.1    | Genera   | al                                         | 9  |

|   | 2.2    | Power I  | Line Routing                               | 9  |

|   | 2.3    | C Pin D  | Decoupling                                 | 9  |

|   | 2.4    | Power    | Supply Decoupling                          | 10 |

|   | 2.5    | Quartz   | Crystal Placement and Signal Routing       | 11 |

|   | 2.6    | Other d  | documents                                  | 12 |

|   | 2.7    | MCU P    | in Summary                                 | 12 |

| 3 | POR    | T INPUT  | Γ / UNUSED PINS                            | 14 |

|   | 3.1    | Port Inp | put                                        | 14 |

|   | 32     | Unused   | 1 Pins                                     | 14 |

# 0 Introduction

This application note describes how to set up a hardware environment for Fujitsu 16LX MCUs. As an example the MB90F34x MCU is used.

# 1 Minimal System

#### THIS CHAPTER GIVES AN EXAMPLE OF A MINIMUM HARDWARE SYSTEM

#### 1.1 Schematic

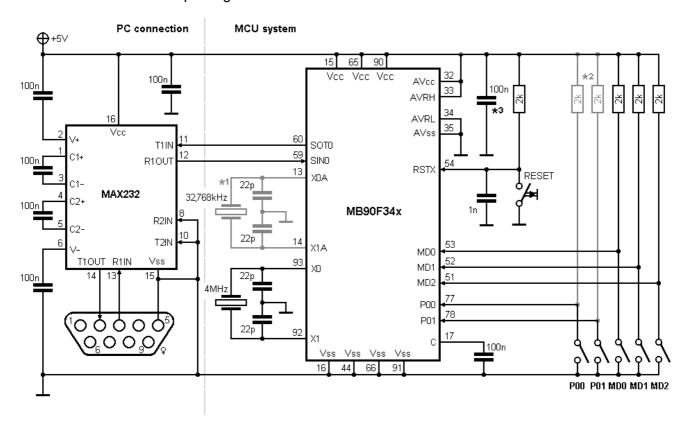

The following graphic shows a schematic of a minimum hardware system. Note that for other MCU families a different pinning is needed.

- \*1 only needed for non-S-Devices.

- \*2 only needed if other than asynchronous programming is used

#### 1.2 Serial Interface

The "PC connection" section is only needed, if no 5V external serial data lines for programming are existing. The MAX232 is a standard level shifter, which converts the 5V levels of the MCU to  $\pm 12V$  RS232V24 levels and vice versa.

If you use a 3.3V MCU a MAX3232 is recommend.

# 1.3 Power supply

The power supply should be 5 Volts  $\pm 10\%$  for normal usage. If a different supply voltage is used please refer to the MB90340 data sheet.

# 1.4 Analog Digital Converter Supply Pins

The analog converter supply pins (AVcc, AVss, AVRH, AVRL) should be connected even if the ADC of the MCU is not used. Please refer to our application note *an-900084-ADC* for using the ADC and pin connection.

<sup>\*3</sup> please refer to chapter 2

#### 1.5 Analog Input Pins

Because the ADC works with an internal sample capacitor the input impedance and external capacity must be low. Fujitsu recommends an input impedance of not more than 15k Ohm. Choose the external capacity as low as possible (about 1 nF for EMI protection).

#### 1.6 Reset Pin (RSTX)

The reset pin should be pulled up to Vcc with a 2-5k resistor. To reset the MCU a switch connects this pin to Vss (Ground). Additionally a capacitor has to be connected between Vss and the reset pin for debouncing the switch and for EMI protection. From experience Fujitsu recommend a capacity of not more than 1 nF. This capacity covers the most common frequency protection in a wide range. Higher capacities and high impedance may cause latch-up effects together with a RSTX-Switch and low EMI protection.

If the device has a HSTX pin, this pin should be connected to RSTX.

#### **Exception:**

Using MB90F548*GHDS* please refer to the data sheet and hardware manual for HSTX and RTSX pin connection and behavior.

For further information please refer to the general application note an-reset-16lx-900074.

#### 1.7 C Pin

A 100nF capacitor *must* be connected to the C pin of the MCU. Otherwise the MCU may not operate correct or will be damaged in worst case. Also see chapter 2.

#### 1.8 Clock Source

A clock source must be provided to the MCU. Therefore crystals or external clock signals can be used. For external source pin X0 (X0A) is used whereby pin X1 (X1A) is not connected.

Note, that for non-S-devices (Families: MB90[F]54x, MB90[F]57x, MB90[F]58x) the 32768Hz sub clock *must* be connected.

Please also refer to the chapter *Outline/Precautions for Device Handling* in the corresponding hardware manual for details.

#### 1.9 Mode Pins

The mode pins signalize the MCU the current operation mode. For a minimal system only two modes are necessary: Flash-Asynchronous-Serial-Programming-Mode and Free-Running-Mode. They should be pulled-up with 2k resistors.

If other programming modes are used, which needs a high level on the port pins (P00, P01), these pins has to pulled-up with a 2k resistor, if using a switch. (Be aware that the port pins then have a different electrical character if used as outputs.)

For these programming modes and methods please refer to the application notes *an-900031-flash-prog* and *an-900095-flash prog2*.

The following settings are used for the both modes mentioned above:

# 1.9.1 Flash-Asynchronous-Serial-Programming-Mode

| P00    | P01    | MD0    | MD1  | MD2  |

|--------|--------|--------|------|------|

| closed | closed | closed | open | open |

# 1.9.2 Free-Running-Mode

| P00  | P01  | MD0  | MD1  | MD2    |

|------|------|------|------|--------|

| open | open | open | open | closed |

# **1.10 NC Pins**

Please read Chapter 3 for how to proceed with unused (not connected) pins.

# 2 Layout and Electromagnetic Compatibility

#### THIS CHAPTER GIVES SOME TIPS FOR LAYOUT DESIGN

#### 2.1 General

To avoid ESD problems and noise emission of the system some rules for the layout design has to be observed.

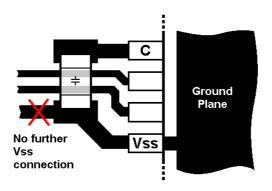

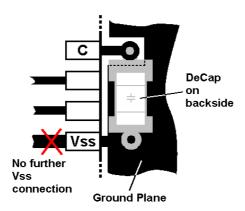

The most critical point is the C pin because this is the connection to the internal 3.3V supply for the MCU core. Thus a decoupling capacitor has to be placed very near to this pin.

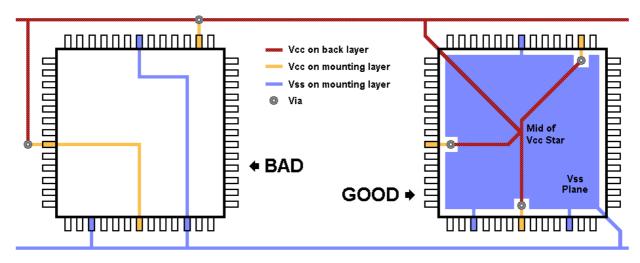

Also the ground and Vcc routing has to be done carefully. Vcc lines should be routed in star shape. We recommend a Vss ground plane *on the mounting side* just under the MCU. For both Vcc and Vss only *one* connection to the rest of the circuit should be done, otherwise noise is carried-over from and to the MCU. Decoupling capacitors (DeCaps) has to be placed as nearest as possible to the related pins. If they are placed too far away their function becomes useless.

If crystals are used, they have to be placed as nearest as possible to the Xn(A) pins.

If possible all decoupling capacitors should be placed on the same mounting side as the MCU.

# 2.2 Power Line Routing

In general the Vcc and Vss lines should not be routed in "chains", but in "star shape". For Vss a ground plane is recommended which covers the chip package, and is connected in *one* point to Vss of the whole circuit.

Below is a example of a bad and a good power line routing:

#### 2.3 C Pin Decoupling

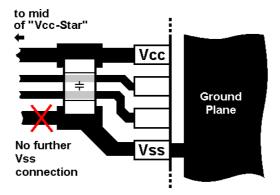

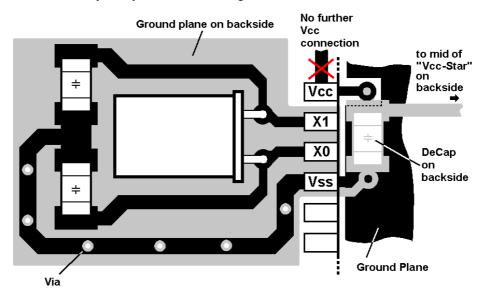

The following routing and placement for single sided metal layer is recommended (Note, that in all following illustrations the mounting metal layer is drawn in black and the back side metal layer in gray):

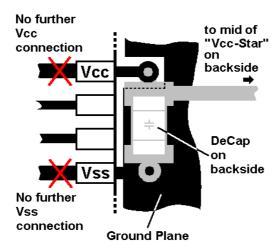

The following routing and placement for double sided metal layer is recommended. Note, that despite the capacitor is placed on the opposite side as the MCU, this solution is the best.

# 2.4 Power Supply Decoupling

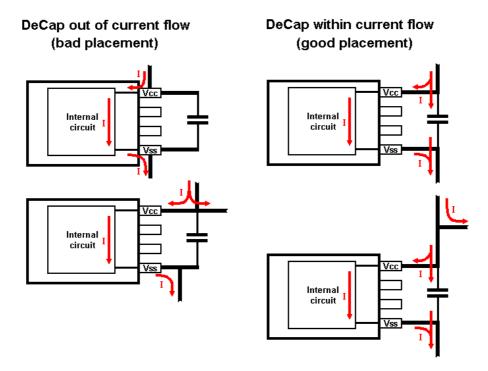

DeCaps for power supply have to be placed within the "current flow". Otherwise they are senseless, because then their function become inoperable. The following graphic illustrates this:

The following routing and placement for single sided metal layer is recommended:

The following routing and placement for double sided metal layer is recommended. Note, that despite the capacitor is placed on the opposite side as the MCU, this solution is the best like for the C pin.

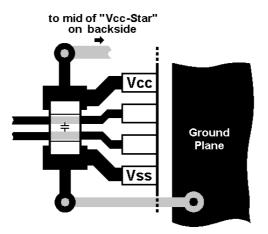

If mounting on both sides is not possible the following placement and routing is recommended:

# 2.5 Quartz Crystal Placement and Signal Routing

The crystal has to be placed as nearest as possible to the MCU. Therefore the oscillator capacitors has to be placed "behind" the crystal.

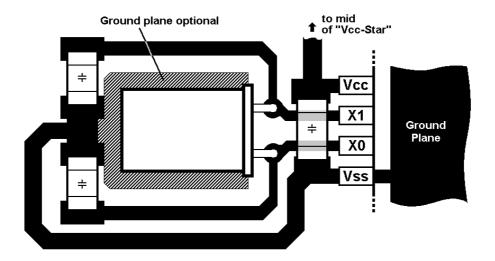

For single metal layer circuit board the following placement and signal routing is recommended:

For double sided metal layer layout the following is recommended:

## 2.6 Other documents

For further detailed information please refer to the application note 16bit-EMC-Guideline.

## 2.7 MCU Pin Summary

The following table shows the EMC critical pins and gives short information about how to connect them.

| Pin name | Function                                                                                                                                         |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VCC      | Main supply for IO buffer MCU core, close to input the internal 3.3V regulator, close to crystal oscillator                                      |  |

| VSS      | Main supply for IO buffer and MCU core, close to the internal 3.3V regulator, close to crystal oscillator                                        |  |

| С        | External smooth capacitor for internal 3.3V regulator output, it is used for supply of the MCU core. Note, that this pin leads the most of noise |  |

| AVCC*           | Power supply for the A/D converter                                                                                                    |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 71100           | 1 one cappy for the fib conferen                                                                                                      |

| AVSS*           | Power supply for the A/D converter                                                                                                    |

| AVRL*           | Reference voltage input for the A/D converter                                                                                         |

| AVRH*           | Reference voltage input for the A/D converter                                                                                         |

| DVCC*,<br>HVCC* | Power supply for the PWM (high current) outputs, it is not connected to VCC, should be connected to extra power supply                |

| DVSS*,<br>HVSS* | Power supply for the PWM (high current) outputs, it is not connected to VSS, should be connected to extra power supply                |

| X0, X0A*        | Oscillator input, if not used so shall be connected with pull-up or pull-down resistor (see please DS)                                |

| X1, X1A*        | Oscillator output, the crystal and bypass capacitor must be connected via shortest distance with X1 pin, if not used so shall be open |

\*only if supported by device

# 3 Port Input / Unused Pins

How to connect Input Port Pins and how to proceed with unused Pins

## 3.1 Port Input

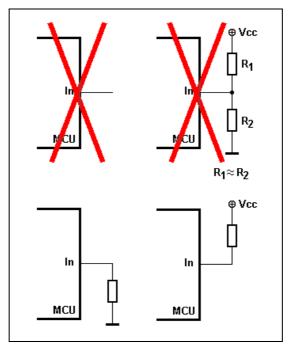

It is strongly recommended to do not leave Input Pins unconnected. In this case those pins can enter a so-called *floating state*. At least this causes a high  $I_{CC}$  current. The worst case is a resulting latch-up effect that may defect the MCU.

Use the internal pull-up resistors, if the port provides such function. If not, use external pull-up or pull-down resistors to define the input-level. If both solutions are not possible, set the Port Pin to Output.

Never connect a potential divider with almost same resistor values.

Be careful with connection of input pins to other devices, which can go into High-Z states. Always use pull-up or pull-down resistors in this case.

#### 3.2 Unused Pins

All pins are set to input after its power-on default. Therefore set unused pins to output or provide them with pull-up or pull-down resistors.