介绍 **dsp** 知识,为大家提供最新的 **dsp** 资讯,更多内容可以去南京研旭电气科技有限公司的官网 <u>www.njyxdq.com</u> <u>www.f28335.com</u> 或者官方论坛,嵌嵌 **dsp** 论坛 <u>www.armdsp.net</u> 进行交流学习

## 欢迎大家收听嵌嵌 dsp 论坛的官方微博

# http://t.qq.com/qianqiandsp

## 还需要什么 **dsp** 资料欢迎加 **QQ**: 1318571484

### 基于 DSP 开发系统设计与实现

摘要:为了设计一个性能稳定的 dsp 开发系统,利用 ti 公司最新推出的 tms320f28335 作为微处理器,该芯片为 32 位浮点型 dsp。在采用浮点 dsp 设计系统时,不需要考虑处理的动态范围和精度,比定点 dsp 在软件编写方面更容易,更适合采用高级语言编程。外围电路主要包含电源电路、ram 扩展电路、晶振电路和复位电路,用来辅助 dsp 的工作。利用电源管理芯片设计电源电路,可以有效解决其他型号的 dsp 对上电顺序的要求;扩展的外部 ram 可以使程序的调试与下载更加方便。利用外部时钟源作为时钟输入,使其输入时钟更加稳定的同时,也可为具有相同时钟的多个 dsp 使用。利用三端监控芯片来实现系统的手动复位和自动复位,使系统的稳定性大大提高。

关键词: tms320f28335; 浮点型; 动态范围; 数字信号处理器

(11gk55) tms320f28335 是 ti 公司最新推出的 32 位浮点型 dsp, 可直接参与浮点型数据的运算, 无需 q 格式的转换, 其主要特点为: 高性能的静态 cmos 技术, 在最高为 150 mhz 振荡频率下, 指令周期为 6.67 ns; 高性能的 32 位 cpu, 单精度浮点运算单元 (fpu), 采用哈佛总线结构, 能快速中断响应和处理, 并有统一的存储器规划, 可用 c/c++语言实现复杂的算法; 控制时钟系统具有片内振荡器和看门狗定时器模块, 支持动态改变锁相环

(p11)的参数值以改变 cpu 的输入时钟频率;8个外部中断,相对于 tms320f281x 系列 dsp,无专门的中断引脚;支持58个外设中断的外设中断扩展寄存器(pie),管理片上外设和外部引脚引起的中断请求;增强型的外设模块;12位 a/d 转换器,可实现16通道的数据转换;88个可编程的分时复用 gpio 引脚;低功耗模式,1.9 v 或1.8 v 内核,3.3 v i/o 供电[1 2]。设计一个集这些优点于一身的 dsp 开发系统,对于初学者和开发人员有着重要的意义。本文首先分析和对比 dsp 电源设计方案,选择合适的设计方案并详细介绍;然后设计存储器扩展电路,并给出其存储范围;通过对比时钟电路的各种实现方案,择优选择适合于该系统的时钟电路并详细介绍;最后给出复位电路的设计方法和提高硬件抗于扰能力的措施。

#### 1系统电源设计

ti 公司的 dsp 系列一般都有独立的内核和 i/o 电源。因为在 dsp 在系统中要承担大量的数据计算,在 cpu 内部,部件的高频率的转换会使系统功耗大大增加[3]。所以采用双

电源的供电方式, f28335 一路为 i/o 提供 3.3 v 电压, 另一路为 cpu 内核提供 1.8 v 或 1.9 v 电压, 这样可大大降低系统的功耗。

电源设计方案一:两路电源独立设计,其优点是调试方便且互不干扰,缺点是不能适合某些对上电次序有要求的 dsp,成本较高。

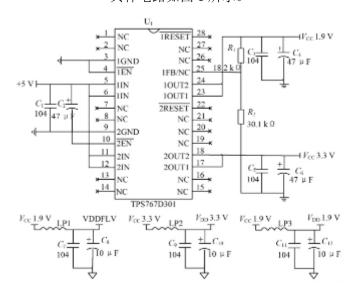

电源设计方案二:采用 ti 公司的双路低压差电压调整器。tps767d3xx 系列电压调整器 是 ti 公司为 dsp 开发的电源管理芯片 [4],通过简单的设计,可以适合某些系列 dsp 内核与 i/o 电压的上电顺序问题。

本设计采用方案二,利用 ti 公司的双路低压差电压调整器 tps767d301。它的特点是: 带有可独立供电的双路输出,一路固定输出为  $3.3\,v$ ,另一路可以在  $1.5\sim5.5\,v$  调整,每路输出电流范围为  $0\sim1\,a$ ; 电压差大小与输出电流成正比,且在最大输出电流为  $1\,a$ 时,最大电压差仅为  $350\,ma$ ; 超低的静态电流  $85\,\mu a$ ,器件无状态时,静态电流仅为  $1\,\mu a$ 。

tms320f28335 对内核和 i/o 的上电顺序没有要求,可以同时上电,使得电源电路大大简化。 具体电路如图 1 所示。

图 1 系统供电电路

tps767d301 的输出端 1out 的电压由式 (1) 确定: vo=vref (1+r1/r2) (1) 式中: vref =1.183 4 v 为电压调整器的内部参考电压; r1 和 r2 的取值应保证驱动电流近似为 50  $\mu$  a。如果电阻过小,会使电流过大,消耗电力; 如果电阻过大,fb 引脚会出现电流脉冲尖峰,会使输出电压波动 [5]。典型电压输出时,r1 和 r2 的取值如表 1 所示。

| 输出电压 /V | $R_1/\mathrm{k}\Omega$ | $R_2/\mathrm{k}\Omega$ |

|---------|------------------------|------------------------|

| 1.9     | 18. 2                  | 30.1                   |

| 2.5     | 33. 2                  | 30.1                   |

| 3.3     | 53.6                   | 30.1                   |

| 3, 6    | 61.9                   | 30.1                   |

| 4.75    | 90.8                   | 30. □                  |

表 1 典型电压输出取样电阻取值

为了提高输出电压的稳定性,模拟电源与数字电源之间通过铁氧体磁珠和电容进行滤波,铁氧体磁珠具有可以忽略的寄生电容,电气特性和一般的电感相似,这样可以减少来自模拟电源或其他并联电路所产生的噪声生干扰。

#### 2系统 ram 扩展

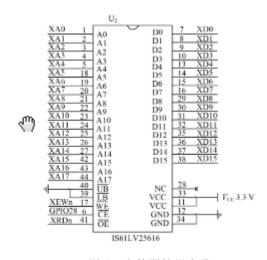

在 tms320f28335 的片上已经集成了 34 k×16 b 的 ram,且内部 ram 的访问速度可达 150 mips,通常用于放置系统对运算速度要求较高的程序。f28335 的片上还集成了 256 k×16 b 的 f1ash,但由于 f1ash 烧写次数有限,而且烧写速度慢,操作麻烦。使用外扩 ram 后,仿真时程序可以放入外扩 ram 中运行,程序长度不受限制,这样程序的设计和调试就非常方便。在调试完成后通过修改.cmd 文件等方法将程序烧进 f1ash 中运行。同时,外扩 ram 还可以开放给其他任务。外扩 ram 选用 issi 公司的 is611v25616,存储容量为 256 k×16 b,3.3 v 的供电电压。使用区间 6 作为外扩存储区间,存储地址范围为 0x100000~0x13ffff。由于is611v25616 的访问速度有 8 ns,10 ns,12 ns,15 ns 可选择,而当 cpu 运行在 150 mhz 时,地址和数据的最小有效时间为 3 个时钟周期,即 20 ns,所以不用考虑时序问题 [6]。存储器的地址线和数据线分别对应 dsp 的地址线和数据线,片选端 cs 和 dsp 的 gpio28 连接,存储器的读/写端口分和 dsp 的读/写端口连接,具体电路图如 2 所示。

图 2 存储器扩展电路

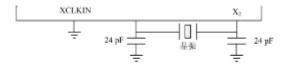

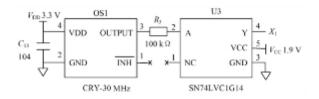

ti的 dsp 时钟电路分为三类: 晶体电路、晶振电路和可编程时钟电路。其中时钟电路如图 3 所示。

图 3 内部时钟源

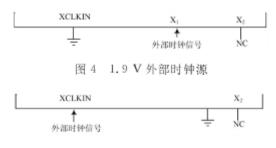

图 3 内部时钟源其特点是:结构简单,但频率范围较小,一般为 20 khz~60 mhz,驱动能力较弱。晶振电路利用外部独立的时钟源给系统提供时钟。其特点是:频率范围较大,一般为 1 hz~400 mhz,驱动能力强,可为具有相同时钟的多 dsp 系统使用。可编程时钟电路可以为外设提供不同的时钟,适用于不同时钟源的系统使用,频带宽度可达 [7] 200 mhz。f28335 的外部时钟可以有两种输入方法,如图 4~图 5 所示。

图 5 3.3 V 外部时钟源

图 41.9 v 外部时钟源图 53.3 v 外部时钟源该设计使用 1.9 v 的外部时钟源晶振电路,如图 6 所示。其中,100  $\omega$  电阻用来衰减外部杂波的干扰,提高时钟波形的质量,sn741vc1g14 是单路施密特反向触发器 [8]。

图 6 晶振电路

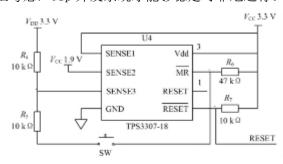

复位电路是在系统上电或程序跑飞时对系统自动或手动的初始化。该设计采用 ti 公司推出的三端监控芯片 tps3307 系列来实现系统初始化和电源监控功能 [9]。 tms320f28335 采用 1.8 v 或 1.9 v 内核电压,3.3 v i/o 电压。利用 tps3307 18 来实现对系统的自动和手动复位。sense1, sense2 和 sense3 管脚分别对 3.3 v i/o 电压、1.8 v 内核电压和 3.3 v 模拟电压监控。手动复位 mr 引脚接至复位键,当按下时 reset 变为低有效,实现手动复位的功能。具体电路如图 7 所示。在上电期间,当电源电压高于 1.1 v 时,reset 开始有效,然后开始监控 sesen 输入管脚的电压。当 sense1,sense2 和 sense3 分别低于门限电压 2.93 v v,1.68 v 和 2.5 v 时,tps3307 18 b reset 向 f28335 发出低电平复位信号,实现自动复位的功能。

#### 5 结语

基于 dsp 开发系统的 pcb 设计对最终系统的性能有着重要的影响。特别是对于 dsp,管脚 多且管脚间的间距小,导致布线时线间距受到限制,容易受到干扰。为了有效抑制干扰,在

布局时输入时钟应尽可能靠近 dsp, 使其输入线路尽可能短, 并使晶振外壳接地; 为了减小芯片上的电源电压瞬时过冲, 在电源的输入端使用去耦电容; 电源是系统的主要干扰源,使用旁路电容及去耦电容来尽量减小电源对系统的影响。在设计中, 可以利用 0.1 μf 的电容来避免内在的振动和高频噪声, 利用 10~100 μf 的旁路电容减小电压输出的脉动 [10]。基于以上考虑, dsp 开发系统才能够稳定可靠地运行。

图 7 复位电路

#### 参考文献

- [1] 雷晓瑜,曹广忠.tms320f28335及其最小应用系统设计[j].电子设计工程,2009,17(1):91 95.

- [2] texas instruments. tms320f2335/28334/28332, tms320 f28235/28234/28232 digital signal controllers  $\lceil r \rceil$ . usa: texas instruments, 2008.

- [3] 汤旭慧. 基于硬件逻辑的微处理器通用开发系统的设计[j]. 现代电子技术,2008,31(2):68 71.

- [4] texas instruments. tps767d301, tps767d317, tps767 d325 dual output low dropout votage regulators  $\[r\]$ . usa: texas instruments, 2003.

- [5] 张云安, 冯志华, 王晓峰. 双路输出低压差电压调整器 tps767d301 及其应用[j]. 电子元器件应用, 2006(7): 112 114.

- [6] 闫晓燕, 张洪亮. 基于 dsp 的高速外扩存储器的设计 [j]. 现代电子技术, 2008, 31 (24): 4 6.

- [7] 王立华, 刘志军. dsp 系统中时钟电路的设计[j]. 电子世界, 2005 (5): 29 30.

- [8] texas instruments. single schmitt trigger inverter  $\[\Gamma\]$ . usa: texas instruments, 2007.

- [9] texas instruments. tp3307 18, tp3307 25, tp3307 33 triple processor supervisors  $\lceil r \rceil$ . usa: texas instruments, 2006.

- [10] 陶涛,赵治华.一种抗强干扰型双面对称布线 pcb 罗氏线圈 [j].电工技术学报,2011,26(9):130 137.

### 相信对你有帮助的:

最实惠的 f28335 系列开发板

基于 DSP28335 的永磁同步电机调速系统设计

基于 DSP 的语音门锁设计与实现

基于 DSP 的图像处理系统的应用研究

基于 TMS320F28335 与 AD7767 高精度数据采集模块设计

介绍 **dsp** 知识,为大家提供最新的 **dsp** 资讯,更多内容可以去南京研旭电气科技有限公司的官网 <u>www.njyxdq.com</u> <u>www.f28335.com</u> 或者官方论坛,嵌嵌 **dsp** 论坛 <u>www.armdsp.net</u> 进行交流学习

欢迎大家收听嵌嵌 dsp 论坛的官方微博

http://t.qq.com/qianqiandsp

还需要什么 dsp 资料欢迎加 QQ: 1318571484