引言

做FPGA研发,知道一点数字电路设计的基础知识是必要的,不然的话会逐渐变成一个会HDL语言的软件工程师,这是我们都不想发生的事情,尤其是对我这样的从软件行业转行过来的人。随着综合工具及自动布局布线工具的快速发展,日益完善与成熟,FPGA工程师跟电路打交道的机会越来越少,致使我们越来越不清楚实际电路的样子了,所以这一节就说一些数字电路的内容,回忆一下数字电路的本来摸样,门电路长什么样;触发器为什么叫‘触发’器;给你一个电路图,怎么得到状态转移图;给你一个实际问题,怎么得到具体电路图,等等这些我们曾经那么熟悉现在又那么模糊的事情。好了,我们开始吧。

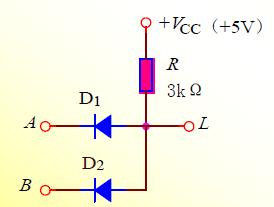

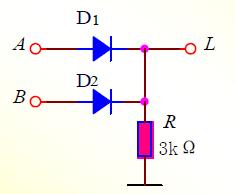

4.1 与,或,非门的实际电路长什么样

与门:

或门:

非门:

4.2 用卡诺图求最简式

例:化简:

画卡诺图:

相同留下,相异去掉,下边那个大圈可得A,左右对称的两个半圈可得D反,

所以最后结果是:

组合逻辑电路的设计,就是给定一个问题,抽象成逻辑表达式,然后用卡诺图化简成最简与或式,然后根据这个式子,把门电路放那,连上线。

其实,逻辑表达式,真值表,卡诺图,波形图,电路图,他们之间可以相互转换。

4.3 触发器发展史

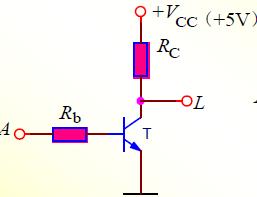

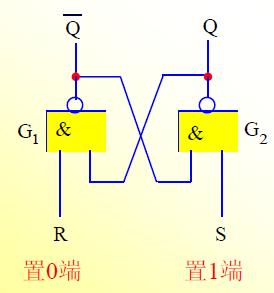

4.3.1 基本RS触发器

1》有两种,两个与非门,两个或非门。下面只说两个与非门的。

2》下面说一下一个“简约而不简单”的问题:触发器,为什么叫“触发器”?

触发触发,一触就爆发的意思。

看上面的电路图,咱们现在触一下S,把S的电压拉低一点;说时迟,那时快,Q就会升高;又一个说时迟,那时快,Q反就会降低;再一个说时迟,那时快,Q又会升高。明眼人已经看出来了,这是“正反馈”,就是“雪崩”啊。我们一触它,它就爆发了,所以就叫触发器。呵呵,解释完毕。

需要注意的是R,S又约束:RS=0。

3》通过上面的电路图,我们可以得到它的真值表:

4》根据这个真值表,我们可以画出卡诺图:

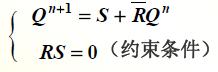

5》化简这个卡诺图,我们可以得到这个触发器的特性方程:

再遵守约束条件的前提下,根据R,S,Qn,利用这个触发器的特性方程,我们就可以知道这个触发器的次态Qn+1。

4.3.2 同步触发器。

为了解决基本触发器的电平直接控制问题而诞生的。

1》给触发器加一个时钟控制端CP,只有在CP端上出现时钟脉冲时, 触发器的状态才能改变。这种触发器称为同步触发器。同步触发器长什么样子呢:

2》同步触发器的特性方程,根据上面基本触发器的步骤,先画真值表,再画卡诺图,然后化简,最后加约束条件,就行了,感兴趣的话,自己动一下手呗。

特性方程和基本RS触发器相同,不过,多了一个约束条件:CP=1时有效。

3》同步触发器的缺点:

空翻问题:由于在CP=1期间,G3 、G4 门都是开着的,都能接收R、S信号,所以,如果在CP=1期间R、S发生多次变化,则触发器的状态也可能发生多次翻转。

什么叫空翻呢?在一个时钟脉冲周期中,触发器发生多次翻转的现象叫做空翻。

4.3.3 中间休息

到目前为止,基本触发器的两个问题,还是没有从根本上解决呢。

一个是电平直接控制问题,同步触发器解决了一点,但是不彻底,又引进了空翻问题。

另外一个是RS有约束的问题。现在还没开始解决。历史的车轮还要向前转啊!

现在鱼与熊掌不可得兼,是先解决约束问题,还是先解决电平控制问题。又两条路摆在面前。

下面就要考虑这两个问题了。

第一条路:先解决电平控制问题:

为了解决电平直接控制问题,和空翻问题,将两个同步RS触发器连起来,又设计出了“主从RS触发器”,但是还是有RS约束的问题,于是为了解决主从RS触发器的RS约束问题,又设计出了“主从JK触发器”。人生没有一帆风顺,主从JK触发器又引进了“一次变化”问题。至此,这条路走完了,失败!

第二条路:先解决RS约束问题:

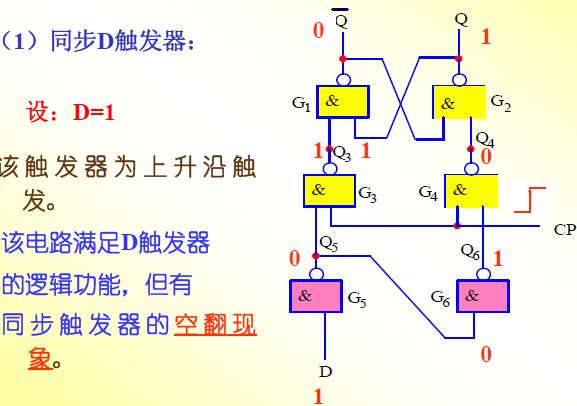

为了解决同步RS触发器的约束问题,在RS之间加了一个非门,产生了同步D触发器。

把两个同步D触发器连起来(或者引入三根反馈线),最终设计出了边沿D触发器。然后将边沿D触发器加以变化,最终设计出了边沿JK触发器。成功!

当然第二条路的成功也离不开第一条路,双管齐下,才取得进展。

还需注意的是,其实边沿触发器有很多种实现方式,为了介绍的思路清晰一点,只说了由两个同步D触发器组成的边沿D触发器。其实,在同步D触发器的基础上引入三根反馈线,解决掉空翻问题,也可组成边沿D触发器。然后进一步组成边沿JK触发器。

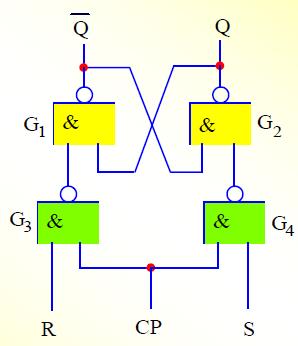

4.3.4 主从RS触发器

两个同步触发器连起来,组成主从RS触发器。有RS约束问题。

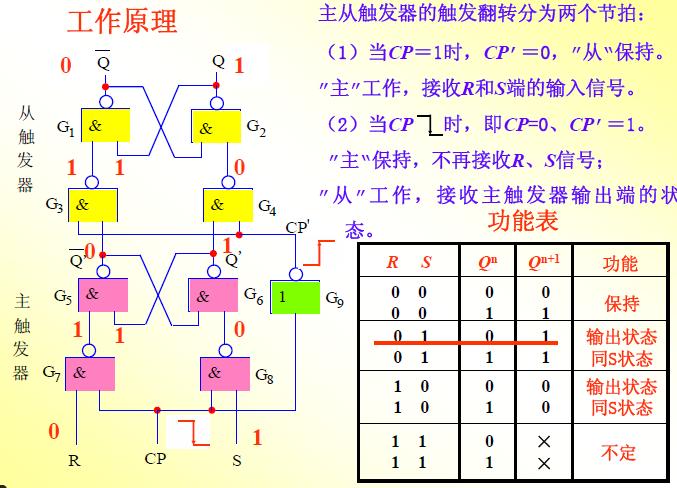

4.3.5 主从JK触发器

解决主从RS触发器的RS约束问题,产生了主从JK触发器。存在一次变化问题。

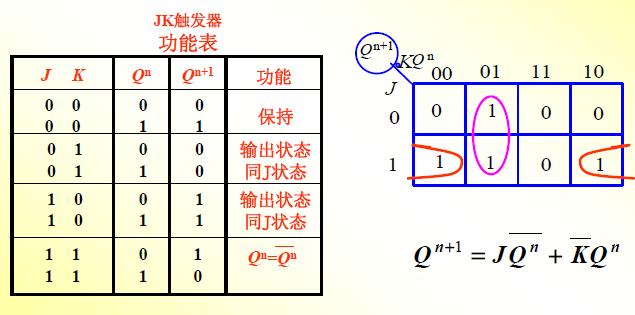

主从JK触发器的特性方程:

先画真值表,再画卡诺图,再化简,最后得到特性方程:

4.3.6 同步D触发器,存在空翻问题。

4.3.7 边沿D触发器

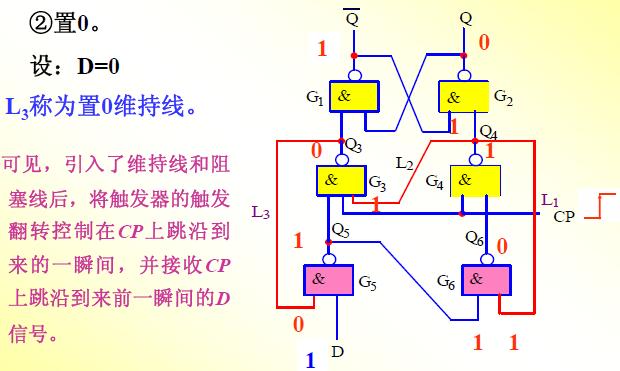

在同步D触发器基础上解决空翻问题,引入三根反馈线。

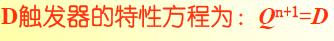

大功告成,需要说的是边沿D触发器的特性方程了:上升沿触发。

4.3.8 D触发器和JK触发器之间的转换

到目前为止,经过漫长的历史长河,我们得到了边沿D触发器,边沿JK触发器。电子市场卖的也就这两种。但是有的时候,只有一种了,肿么办呢,这时就需要转换一下,用现有的一种转换为另外一种。

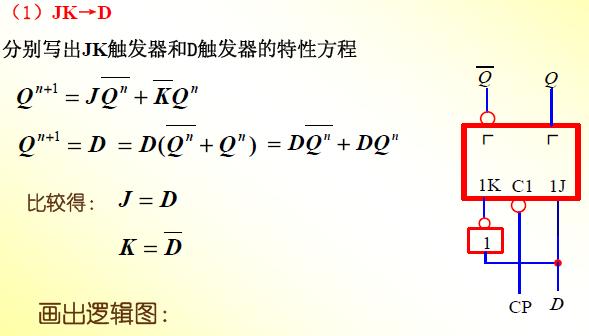

1》 只有卖JK触发器的了,D触发器没货了。JK->D

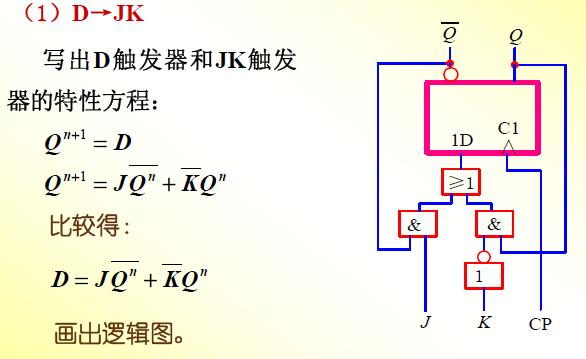

2》 只有卖D触发器的了,JK触发器没货了。D->JK

4.4 时序电路分析与设计

哈哈,终于到真刀真枪的时候了。学了那么多,不就是为了能看懂别人设计的电路,和自己设计电路吗!所以下面就分两方面介绍。没有理论,就两个小例子。

4.4.1 时序电路分析

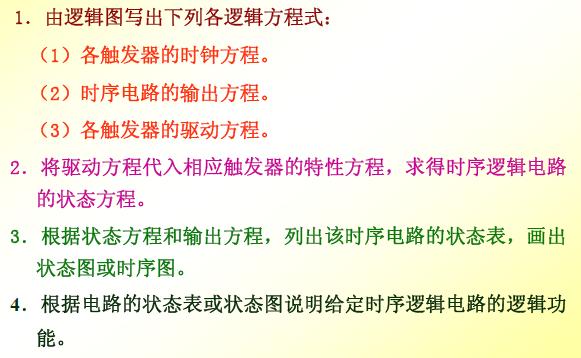

先说一下一般步骤:

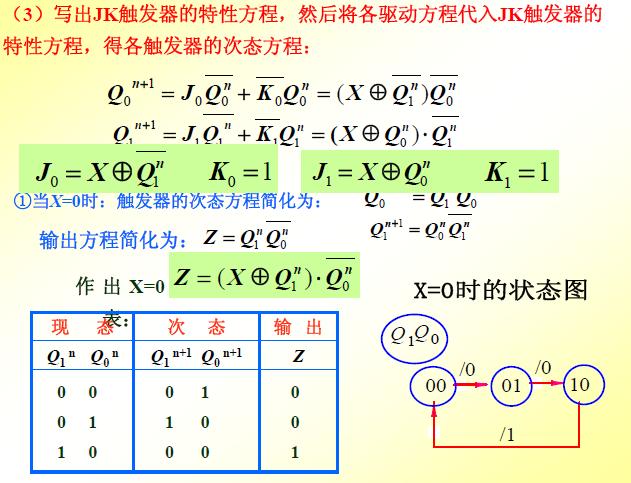

下面就说一个例子:

时序逻辑电路的分析完毕。下面是设计了。

4.4.2 时序电路设计

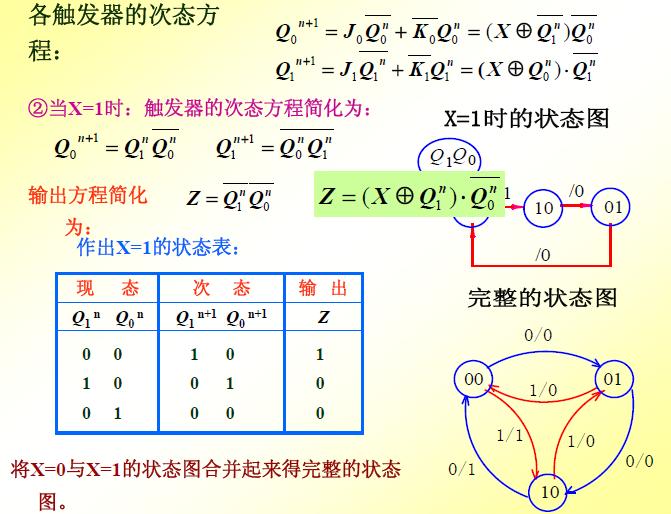

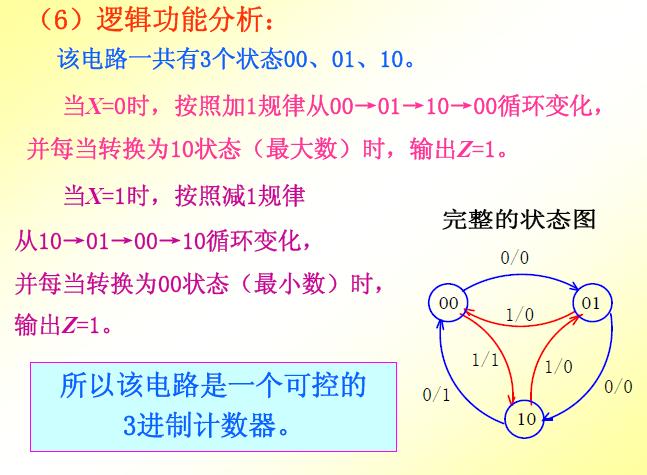

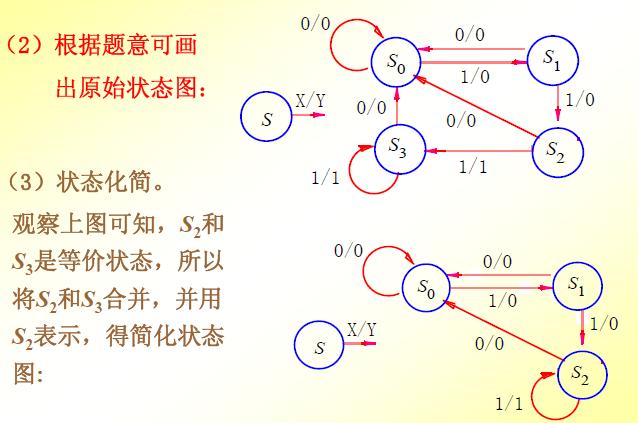

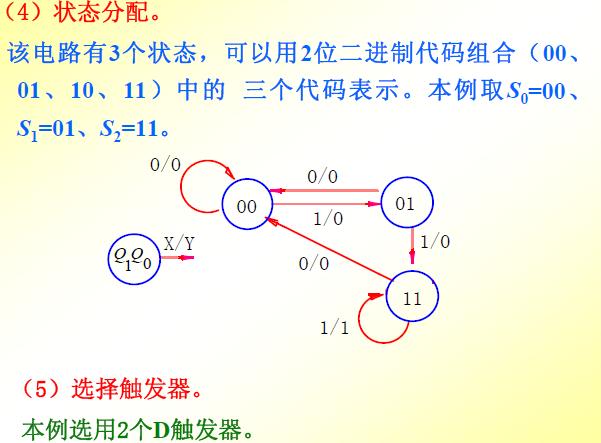

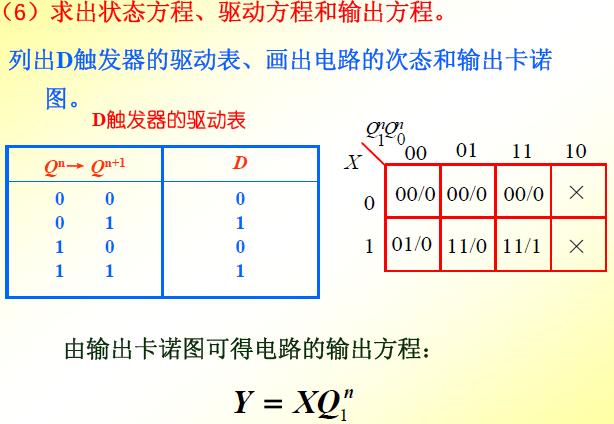

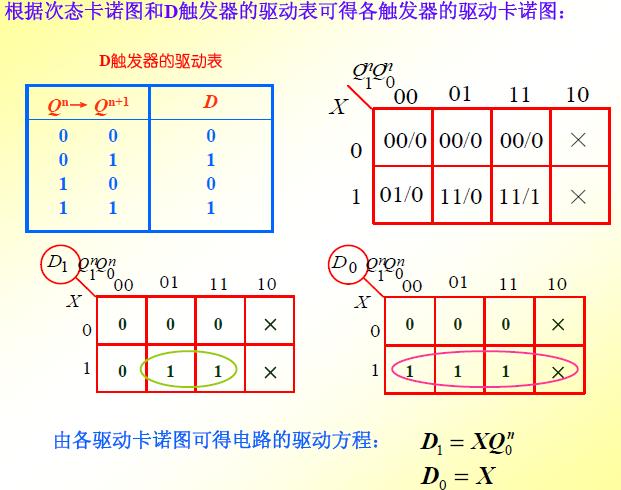

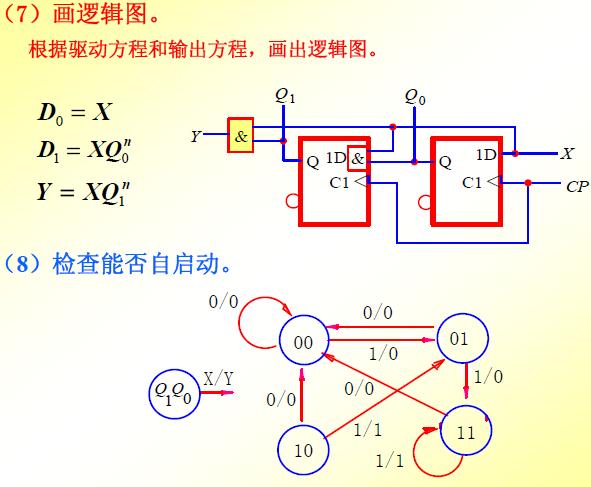

下面是一个例子:

|