克服FPGA I/O引脚分配挑战(08-100)-2

|

- UID

- 1066743

|

克服FPGA I/O引脚分配挑战(08-100)-2

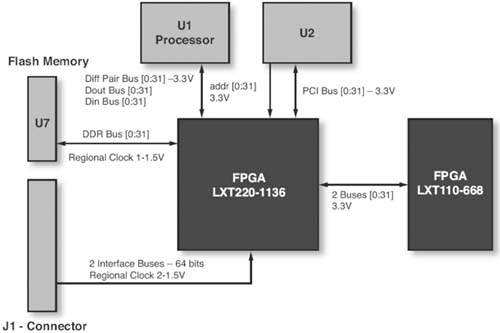

图1 PCB连接图 步骤2: 定义引脚布局要求

一旦了解了主要的FPGA接口并创建了物理布局的原型,就可以定义引脚布局了。 有些设计人员喜欢使用包含所有I/O信号数据表来保持与引脚的对应。 你可以按电压、时钟、接口或总线对它们进行分组。 这一方法确实非常有用,因为它可帮助你将信号组合成组,从而在分配引脚时可以按组进行。 这一阶段,你还会发现为了实现最优PCB布线,有些关键接口必须置于器件的某个边,或者利用外部物理引脚。

在考虑到FPGA和PCB要求并确定了主要的接口位置以后,下一步是根据所有这些条件将引脚分配给I/O组。 这也是真正开始工作的地方。 在当前的设计流程中,引脚分配时一项耗费时间的任务,在解决任何性能和信号完整性问题的过程中可能会涉及许多尝试和错误。 传统上,设计人员都是徒手画图来完成这项任务的,因为EDA和芯片供应商没有提供帮助设计人员将FPGA和PCB引脚布局可视化的工具。

但现在赛灵思公司提供了相应的工具。 在ISE Foundation软件工具10.1版本中包含的PlanAhead Lite是PlanAhead设计、分析和平面布局工具的简化版。 其中包括的针对PCB 和 FPGA设计的PinAhead的工具使得I/O引脚配置更为容易。

这里我们不打算详细介绍该工具的所有细节,而只是看一下如何将其用于I/O引脚分配。 如果你希望了解PinAhead的更详细信息,包括视频展示和教程,请访问 www.xilinx.com/planahead。

步骤3: 利用PinAhead进行引脚分配

PinAhead环境提供了一组不同的视图。利用这些视图可以帮助完成I/O端口信息与物理封装引脚或裸片I/O盘(Pad)的对应和分配(图2)。

PinAhead的图形环境与PlanAhead类似,在器件视图中清晰地显示出芯片上的I/O盘和相关资源,并在封装视图中显示出物理器件引脚。 视图同时显示出I/O端口和物理引脚信息,这样可以通过交叉选取来试探逻辑设计和物理器件资源的对应。 |

|

|

|

|

|