是触发器的两个输出端。当Q=0,

是触发器的两个输出端。当Q=0, =1时,称触发器状态为0,当Q=1,

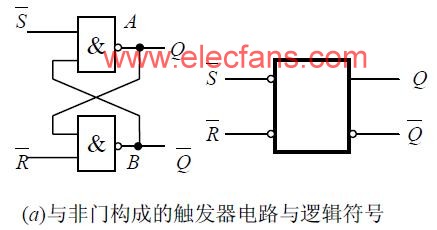

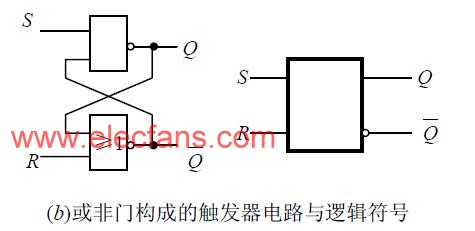

=1时,称触发器状态为0,当Q=1, =Q时,称触发器状态为1。触发器有两个输入端SR、,字母上的非号表示低电平或负脉冲有效(在逻辑符号中用小圆圈表示)。根据与非逻辑关系可写出触发器输出端的逻辑表达式:

=Q时,称触发器状态为1。触发器有两个输入端SR、,字母上的非号表示低电平或负脉冲有效(在逻辑符号中用小圆圈表示)。根据与非逻辑关系可写出触发器输出端的逻辑表达式:

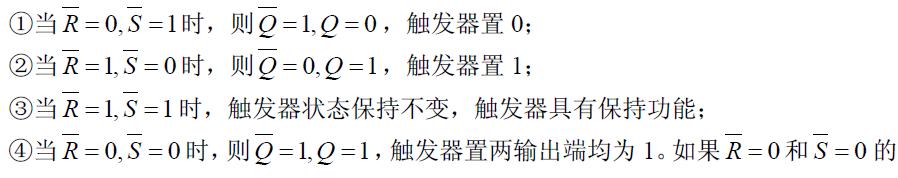

=1的状态。因此,在

=1的状态。因此,在 而且又都同时变为1时,电路的竞争使得最终稳定状态不能确定。这种状态应尽可能避免。但假若

而且又都同时变为1时,电路的竞争使得最终稳定状态不能确定。这种状态应尽可能避免。但假若 后,

后, 和

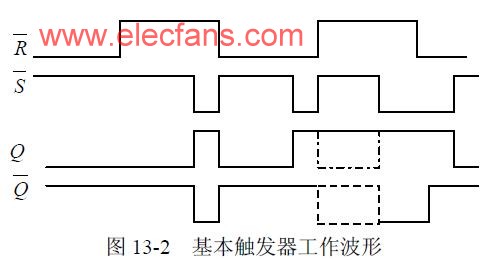

和 不是同时恢复为1,那么最后稳定状态的新状态仍按上述①或②的情况确定,即触发器或被置0或被置1。图13-2所示为基本触发器的工作波形。图中虚线部分表示不确定。

不是同时恢复为1,那么最后稳定状态的新状态仍按上述①或②的情况确定,即触发器或被置0或被置1。图13-2所示为基本触发器的工作波形。图中虚线部分表示不确定。

为置1端,因为

为置1端,因为 =0时被置1,所以是低电平有效。

=0时被置1,所以是低电平有效。 为置0端,因为

为置0端,因为 =0时置0,所以也是低电平有效。基本触发器又称置0置1触发器,或称为RS触发器。

=0时置0,所以也是低电平有效。基本触发器又称置0置1触发器,或称为RS触发器。 =0,

=0, =1,触发器置1后,如果

=1,触发器置1后,如果 由0恢复至1,即

由0恢复至1,即 =1,

=1, =1,触发器保持在1状态,即Q=1。同理,当

=1,触发器保持在1状态,即Q=1。同理,当 =1,

=1, =0时,触发器置0后,

=0时,触发器置0后, 由0恢复至1,即

由0恢复至1,即 =1,

=1, =1时,触发器保持在0状态,即Q=0。这一保持功能和前面介绍的组合电路是完全不同的,因为在组合电路中,如果输入信号确定后,将只有唯一的一种输出。

=1时,触发器保持在0状态,即Q=0。这一保持功能和前面介绍的组合电路是完全不同的,因为在组合电路中,如果输入信号确定后,将只有唯一的一种输出。| 欢迎光临 电子技术论坛_中国专业的电子工程师学习交流社区-中电网技术论坛 (http://bbs.eccn.com/) | Powered by Discuz! 7.0.0 |