锁相环(PLL)和混合模式时钟管理器(MMCM)处理的工作有许多是相同的,比如频率综合、内外部时钟抖动滤波、时钟去歪斜等。这两种资源也可用于镜像、发送或再缓冲时钟信号。

锁相环(PLL)和混合模式时钟管理器(MMCM)处理的工作有许多是相同的,比如频率综合、内外部时钟抖动滤波、时钟去歪斜等。这两种资源也可用于镜像、发送或再缓冲时钟信号。 一般来说,DLL与PLL类似。但与PLL不同的是DLL不含压控振荡器(VCO)。PLL会一直存储相位和频率信息,而DLL只存储相位信息。因此,DLL略比PLL稳定。DLL和PLL这两种类型都可以使用模拟和数字技术设计,或者混合两种技术设计。但赛灵思器件中的DCM采用全数字化设计。

一般来说,DLL与PLL类似。但与PLL不同的是DLL不含压控振荡器(VCO)。PLL会一直存储相位和频率信息,而DLL只存储相位信息。因此,DLL略比PLL稳定。DLL和PLL这两种类型都可以使用模拟和数字技术设计,或者混合两种技术设计。但赛灵思器件中的DCM采用全数字化设计。 混合模式时钟管理器

混合模式时钟管理器

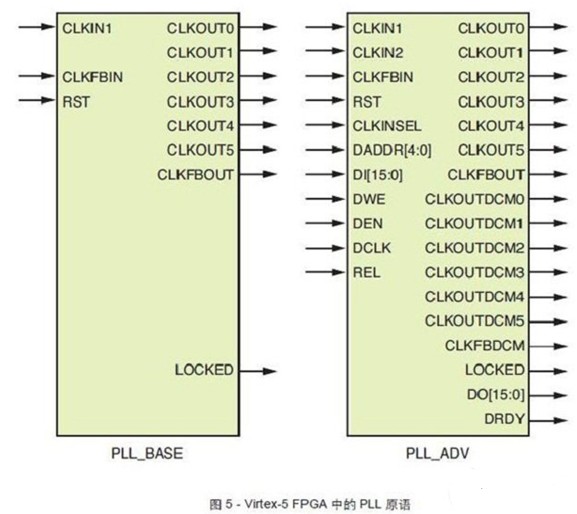

锁相环

锁相环 设计移植

设计移植| 欢迎光临 电子技术论坛_中国专业的电子工程师学习交流社区-中电网技术论坛 (http://bbs.eccn.com/) | Powered by Discuz! 7.0.0 |