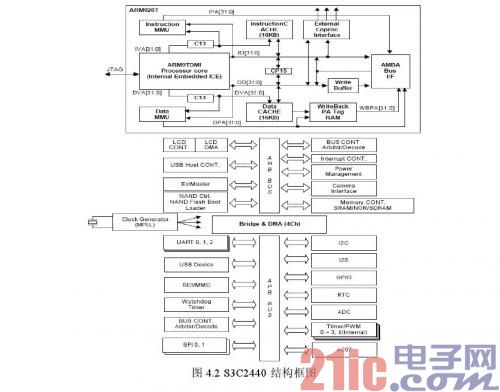

S3C2440X芯片集成了大量的功能单元,包括:

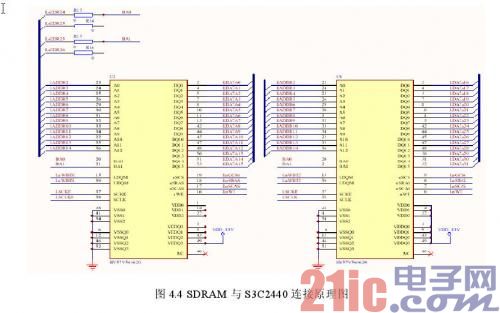

S3C2440X芯片集成了大量的功能单元,包括: 与FLASH存储器相比较,SDRAM不具有掉电保持数据的特性,但其存取速度大大高于FLASH存储器,且具有读、写属性。因此,SDRAM在系统中主要用做程序的运行空间、数据及堆栈区。当系统启动时,CPU首先从复位地址0X0处读取启动代码,在完成系统的初始化后,程序代码一般调入SDRAM中运行,以提高系统的运行速度;同时,系统及用户堆栈、运行数据也都放在SDRAM中。SDRAM具有单位空间存储容量大、价格便宜的优点,已广泛应用在各种嵌入式系统中。SDRAM的存储单元可以理解为一个电容,总是倾向于放电,为避免数据丢失,必须定时刷新(充电)。因此,要在系统中使用SDRAM,就要求微处理器具有刷新控制逻辑,或在系统中另外加入刷新控制逻辑电路。S3C2440微处理器片内具有独立的SDRAM刷新控制逻辑,可方便地与SDRAM接口相连。目前常用的SDRAM为16位数据宽度,工作电压一般为3.3 V.本系统中使用HY57V561620作为SDRAM,其基本特性为:工作电压为3.3 V,按4Bank *4M *16 Bit方式组织,单片存储容量为32 MB,支持自动刷新( Auto-Refresh )和自刷新(Self-Refresh )功能,16位数据宽度。如图4.4所示为S3C2440和HY57V561620的连接电路原理图。

与FLASH存储器相比较,SDRAM不具有掉电保持数据的特性,但其存取速度大大高于FLASH存储器,且具有读、写属性。因此,SDRAM在系统中主要用做程序的运行空间、数据及堆栈区。当系统启动时,CPU首先从复位地址0X0处读取启动代码,在完成系统的初始化后,程序代码一般调入SDRAM中运行,以提高系统的运行速度;同时,系统及用户堆栈、运行数据也都放在SDRAM中。SDRAM具有单位空间存储容量大、价格便宜的优点,已广泛应用在各种嵌入式系统中。SDRAM的存储单元可以理解为一个电容,总是倾向于放电,为避免数据丢失,必须定时刷新(充电)。因此,要在系统中使用SDRAM,就要求微处理器具有刷新控制逻辑,或在系统中另外加入刷新控制逻辑电路。S3C2440微处理器片内具有独立的SDRAM刷新控制逻辑,可方便地与SDRAM接口相连。目前常用的SDRAM为16位数据宽度,工作电压一般为3.3 V.本系统中使用HY57V561620作为SDRAM,其基本特性为:工作电压为3.3 V,按4Bank *4M *16 Bit方式组织,单片存储容量为32 MB,支持自动刷新( Auto-Refresh )和自刷新(Self-Refresh )功能,16位数据宽度。如图4.4所示为S3C2440和HY57V561620的连接电路原理图。

| 欢迎光临 电子技术论坛_中国专业的电子工程师学习交流社区-中电网技术论坛 (http://bbs.eccn.com/) | Powered by Discuz! 7.0.0 |