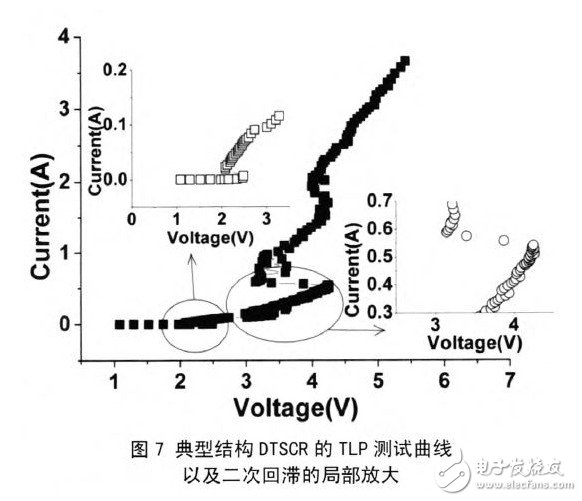

3 DTSCR结构概述LVTSCR能够做到相同工艺下GGNMOS相近的触发电压,但如果需要得到更低的触发电压用于极低电压电路的ESD保护,则需要改变 SCR的触发方式。通过外加辅助触发结构,SCR的开启电压是可以得到控制的。二极管辅助触发的SCR(DTSCR)就是一种更有着低电压开启特性的 SCR结构,其剖面示意图如图6所示。

| 欢迎光临 电子技术论坛_中国专业的电子工程师学习交流社区-中电网技术论坛 (http://bbs.eccn.com/) | Powered by Discuz! 7.0.0 |