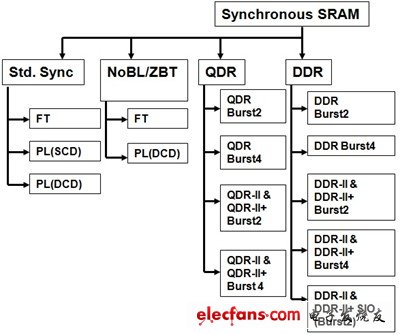

图1:同步SRAM种类

ipelined

ipelined QDR SRAM

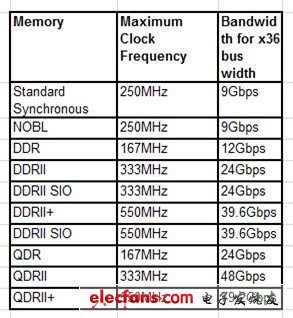

QDR SRAM表 1: 同步SRAM 带宽概览

另一个同步SRAM的选择因素是功耗。QDR/DDR器件的功率消耗比标准同步SRAM要低,因为供电电压低。决定存储器选择的其他因素如表2所示:

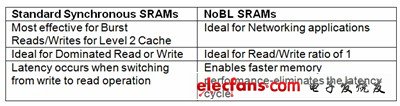

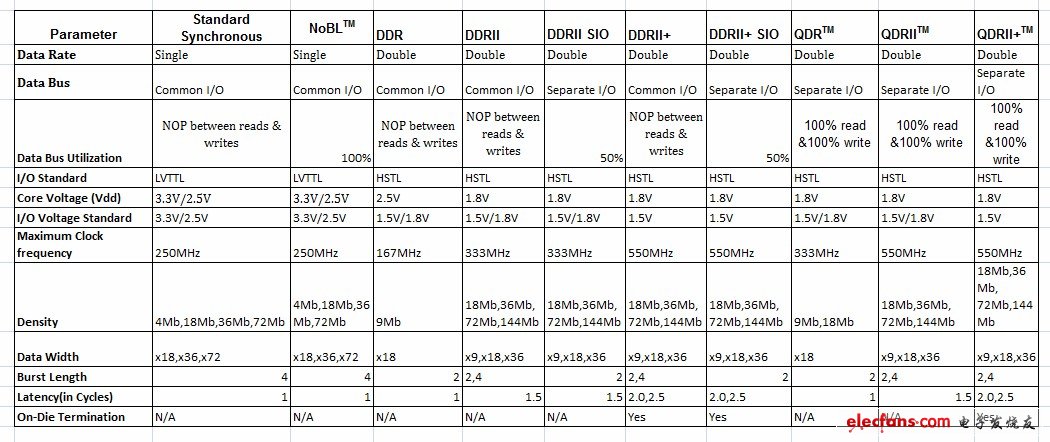

另一个同步SRAM的选择因素是功耗。QDR/DDR器件的功率消耗比标准同步SRAM要低,因为供电电压低。决定存储器选择的其他因素如表2所示:表2:存储器选择概览

注:QDRII+ 和DDRII+可以提供带活不带ODT (On-Die Termination)

注:QDRII+ 和DDRII+可以提供带活不带ODT (On-Die Termination)| 欢迎光临 电子技术论坛_中国专业的电子工程师学习交流社区-中电网技术论坛 (http://bbs.eccn.com/) | Powered by Discuz! 7.0.0 |