图1 逻辑单元的ROM和CAM

存储器的复杂性和独特性表明,采用存储器编译器并不完全可行,每种嵌入式存储器都需要采用新的电路技术来设计,以便满足微处理器的高性能、高密度、低功耗和极低噪声的要求。

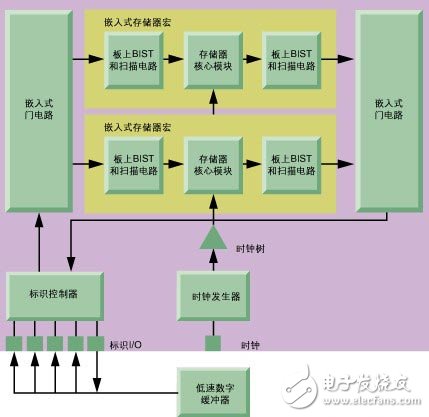

图2 验证存储器设计

现在,要驱动500MHz的外部I/O引脚很不实际,我们设计了专用嵌入式ATE电路来俘获并评估嵌入式宏的实际存取时间。通过建立片上测试器,可确保采用低成本的数字测试器来驱动及评测芯片。

图3 采用集总和加载技术

集总和加载方法是通用技术,面临分布式载荷造成的模型不精确的问题,并受到由阻容(RC)网络引起的传输线效应的影响。RC网络不仅包含阻容元件,还包含要对栅极、源极和漏极电容精确建模的晶体管。为了获得精确时序,要建立验证关键路径中所有元件与实际宏的LPE网表之间匹配程度的工具。对我们感兴趣的节点,要比较关键路径和LPE网表之间的引线、栅极、源极、漏极、耦合电容和电阻。当这些参数不匹配时,就必须修正负载模型。| 欢迎光临 电子技术论坛_中国专业的电子工程师学习交流社区-中电网技术论坛 (http://bbs.eccn.com/) | Powered by Discuz! 7.0.0 |