(c)遮罩示意圖

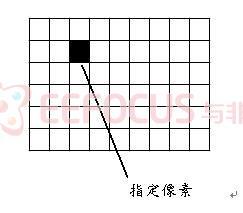

圖2.1 遮罩器與指定像素

2.1 高通濾波器及低通濾波器

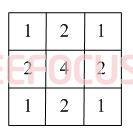

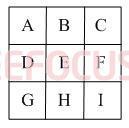

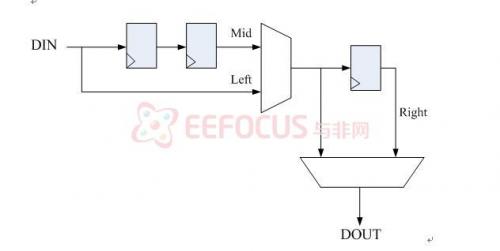

圖2.4 拆解後濾波器示意圖

圖 2.5 指定像素在邊界

圖2.6 週期性對稱延伸示意圖

第三章 硬體功能及規格表3.1 LPF輸入及輸出腳位

| 輸入腳位名稱 | 功能說明 | 大小(bits) |

| CLK | 時脈週期。 | 1 |

| RSTn | 重設,0代表重設;1代表不動作。 | 1 |

| DIN | 接收輸入資料。 | 24 |

| DINEn | 控制輸入資料的致能;0 代表致能。 | 1 |

| HS | 當資料為圖片每行的開頭之前或結尾之後則1;否則0。 | 1 |

| VS | 當資料為圖片的開頭之前或結尾之後則1;否則0。 | 1 |

| 輸出腳位名稱 | 功能說明 | 大小(bits) |

| DOUT | 傳送輸出資料。 | 24 |

| DOUTEn | 控制輸出資料的致能;0 代表致能。 | 1 |

圖3.2 YUV共用示意圖

圖3.3內部架構示意圖

表3.2

輸入腳位名稱 | 功能說明 | 大小(bits) |

CLK | 時脈週期。 | 1 |

RSTn | 重設,0代表重設;1代表不動作。 | 1 |

HS | 當資料為圖片每行的開頭之前或結尾之後則1;否則0。 | 1 |

VS | 當資料為圖片的開頭之前(或結尾之後)則1;否則0。 | 1 |

DINEn | 控制輸入資料的致能;0 代表致能。 | 1 |

DIN_1 | 從SRAM讀進的偶數列資料。 | 16 |

DIN_2 | 從SRAM讀進的奇數列資料。 | 16 |

DIN_3 | 從掃描列讀進的資料。 | 16 |

輸出腳位名稱 | 功能說明 | 大小(bits) |

DOUTEn | 控制輸出資料的致能;0 代表致能。 | 1 |

DOUT_1 | 僅含有Y且送到Processer的資料。 | 8 |

DOUT_2 | 僅含有Y且送到Processer的資料。 | 8 |

DOUT_3 | 僅含有Y且送到Processer的資料。 | 8 |

DOUT_4 | 僅含有U的資料。 | 8 |

DOUT_5 | 僅含有V的資料。 | 8 |

C_EVEN | 0代表掃瞄列為偶數列;1則為奇數列。 | 1 |

表3.3

輸入腳位名稱 | 功能說明 | 大小(bits) |

CLK | 時脈週期。 | 1 |

RSTn | 重設,0代表重設;1代表不動作。 | 1 |

DINEn | 控制輸入資料的致能;0 代表致能。 | 1 |

DIN | 寫入到記憶體的資料。 | 32 |

C_EVEN | 0代表掃瞄列為偶數列;1則為奇數列。 | 1 |

輸出腳位名稱 | 功能說明 | 大小(bits) |

DOUT | 從記憶體讀出的資料。 | 32 |

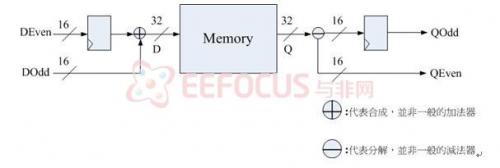

圖3.6 SRAM儲存方式

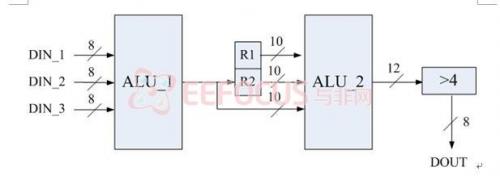

圖3.7 計算處理器

表3.4

輸入腳位名稱 | 功能說明 | 大小(bits) |

CLK | 時脈週期。 | 1 |

RSTn | 重設,0代表重設;1代表不動作。 | 1 |

DIN_1 | 僅含有Y且加權值為1。 | 8 |

DIN_2 | 僅含有Y且加權值為2。 | 8 |

DIN_3 | 僅含有Y且加權值為1。 | 8 |

輸出腳位名稱 | 功能說明 | 大小(bits) |

DOUT | 輸出為計算過後的Y。 | 8 |

圖4.1 上下週期性對稱示意圖

圖4.2 左右週期性對稱示意圖

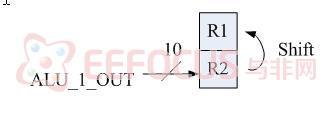

圖4.3 處理左右邊界問題之架構

圖4.4 記憶體輸入之合成與輸出之分解

(a) (b)

(c)

圖4.5 拆解步驟

圖4.6 計算處理器內部

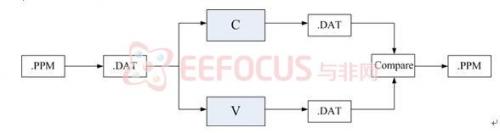

圖5.2 模擬及驗證流程

圖5.3(a) 低通濾波器

圖5.3(b) 低通濾波器

圖5.4 邊界處理器

圖5.5(a) 儲存偶數列之記憶體

圖5.5(b) 儲存偶數列之記憶體

圖5.6 計算處理器

圖5.7 含有雜訊之影像(未處理)

圖5.8 影像經過第一次處理

圖5.9 影像經過第二次處理

| 欢迎光临 电子技术论坛_中国专业的电子工程师学习交流社区-中电网技术论坛 (http://bbs.eccn.com/) | Powered by Discuz! 7.0.0 |