| 注意 | 在数据和指令域分离的系统中,如ARM940T,在指令和数据域中都要有一个有效域被预先设定好。 |

| 注意 | 在数据和指令分离的系统中,通过MRC和MCR指令的第二个操作数<opcode2>来决定读写D-Cache和I-Cache属性。 |

| Cache位 | 写缓存区位 | 域 属 性 |

| C=0 | B=0 | 禁止Cache、禁止写缓存 |

| C=0 | B=1 | 禁止Cache、使能写缓存 |

| C=1 | B=0 | 使能Cache,域使用回写策略 |

| C=10 | B=1 | 使能Cache,域使用直写策略 |

| AP编码 | 管 理 者 | 用 户 |

| 00 | 不可访问 | 不可访问 |

| 01 | 读/写 | 不可访问 |

| 10 | 读/写 | 只读 |

| 11 | 读/写 | 读/写 |

| 注意 | 对于Arm946E-S和Arm1026EJ-S两个内核版本,它们的访问权限机制更复杂,采用的是扩展AP,扩展组AP位域编码支持两个增强的权限域,对其进行操作的MRC和MCR指令形式更复杂,有关更详细的内容,请参加Arm公司的用户手册。 |

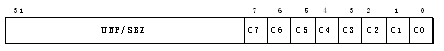

| 位 名 称 | 对 应 位 | 注 释 |

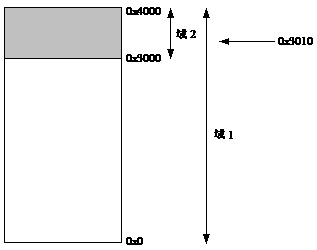

| 起始地址 | [31:12] | 保护域的第一个字节起始地址,具体见表2.18 |

| SBZ | [11:6] | 必须设为0 |

| Size | [5:1] | 设Size=N,则域尺寸为2N+1,其中11≤N≤31 |

| E | [0] | 域使能,E=1使能,E=0禁止 |

| Size(bits[5:1]) | 域 尺 寸 | 起始地址(bits[31:12]) |

| 0b00000~0b01010 | 未定义 | - |

| 0b01011 | 4KB | 无 |

| 0b01100 | 8KB | bit[12]必须为0 |

| 0b01101 | 16KB | bits[13:12]必须为0 |

| 0b01110 | 32KB | bits[14:12]必须为0 |

| 0b01111 | 64KB | bits[15:12]必须为0 |

| 0b10000 | 126KB | bits[16:12]必须为0 |

| 0b10001 | 256KB | bits[17:12]必须为0 |

| 0b10010 | 512KB | bits[18:12]必须为0 |

| 0b10011 | 1MB | bits[19:12]必须为0 |

| 0b10100 | 2MB | bits[20:12]必须为0 |

| 0b10101 | 4MB | bits[21:12]必须为0 |

| 0b10110 | 8MB | bits[22:12]必须为0 |

| 0b10111 | 16MB | bits[23:12]必须为0 |

| 0b11000 | 32MB | bits[24:12]必须为0 |

| 0b11001 | 64MB | bits[25:12]必须为0 |

| 0b11010 | 128MB | bits[26:12]必须为0 |

| 0b11011 | 256MB | bits[27:12]必须为0 |

| 0b11100 | 512MB | bits[28:12]必须为0 |

| 0b11101 | 1GB | bits[29:12]必须为0 |

| Size(bits[5:1]) | 域 尺 寸 | 起始地址(bits[31:12]) |

| 0b11110 | 2GB | bits[30:12]必须为0 |

| 0b11111 | 4GB | bits[31:12]必须为0 |

| 欢迎光临 电子技术论坛_中国专业的电子工程师学习交流社区-中电网技术论坛 (http://bbs.eccn.com/) | Powered by Discuz! 7.0.0 |