| 写 策 略 | 直 写 法 | 回 写 法 |

| 可靠性 | 高 | 低 |

| 与主存的通信量 | 多 | 少 |

| 控制的复杂性 | 简单 | 复杂 |

| 硬件实现代价 | 大 | 小 |

| 内 核 | 写 策 略 | 替 换 策 略 |

| ARM720T | 直写法 | 随机 |

| ARM740T | 直写法 | 随机 |

| ARM920T | 直写法、回写法 | 随机、轮转 |

| ARM940T | 直写法、回写法 | 随机 |

| ARM926EJ-S | 直写法、回写法 | 随机、轮转 |

| ARM946E | 直写法、回写法 | 随机、轮转 |

| ARM1020E | 直写法、回写法 | 随机、轮转 |

| ARM1026EJS | 直写法、回写法 | 随机、轮转 |

| Intel Strong ARM | 回写法 | 轮转 |

| Intel Xscale | 直写法 | 轮转 |

| 相 关 位 | 作 用 |

| C(bit[2]) | 当数据Cache和指令Cache分开时,本控制位禁止/使能数据Cache 当数据Cache和指令Cache统一时,本控制位禁止/使能整个Cache 0:禁止Cache 1:使能Cache 如果系统中不含Cache,读取时该位返回0,写入时忽略该位 当系统中Cache不能禁止时,读取返回1,写入时忽略该位 |

| 相 关 位 | 作 用 |

| I(bit[12]) | 当数据Cache和指令Cache是分开的,本控制位禁止/使能指令Cache 0:禁止指令Cache 1:使能指令Cache 如果系统中使用统一的指令Cache和数据Cache或者系统中不含Cache,读取该位时返回0,写入时忽略该位 当系统中的指令Cache不能禁止时,读取该位返回1,写入时忽略该位 |

| RR(bit[14]) | 如果系统中Cache的淘汰算法可以选择的话,本控制位选择淘汰算法 0:选择常规的淘汰算法,如随机淘汰算法 1:选择预测性的淘汰算法,如轮转(round-robin)淘汰算法 如果系统中淘汰算法不可选择,写入该位时被忽略,读取该位时,根据其淘汰算法可以简单地预测最坏情况,并返回1或者0 |

| 注意 | c7有时也用于其他相似的功能,如果系统中存在预测缓存(prefetch buffers)和分支目标(branch target)Cache,c7也将负责对它们进行控制。 |

| CRm | Opcode2 | 含 义 | 数 据 |

| c0 | 4 | 等待中断 | 0(SBZ,should be zero) |

| c5 | 0 | 使整个指令Cache无效 | 0 |

| c5 | 1 | 使指令Cache中某行无效 | 虚拟地址 |

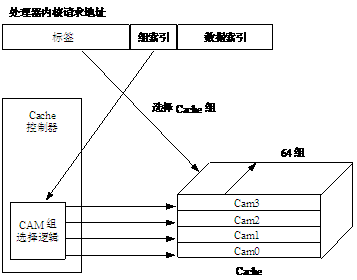

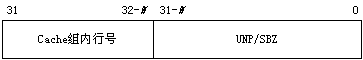

| c5 | 2 | 使指令Cache中某行无效 | 组号/索引 |

| c5 | 4 | 清空预取缓存区 | 0 |

| c5 | 6 | 清空整个分支目标Cache | 0 |

| c5 | 7 | 清空分支目标Cache中的某入口项 | 生产商定义 |

| c6 | 0 | 使整个数据Cache无效 | 0 |

| CRm | Opcode2 | 含 义 | 数 据 |

| c6 | 1 | 使数据Cache中的某行无效 | 虚拟地址 |

| c6 | 2 | 使数据Cache中的某行无效 | 组号/索引 |

| c7 | 0 | 使整个统一Cache无效 哈佛结构中,使整个数据Cache和指令Cache无效 | 0 |

| c7 | 1 | 使统一Cache中某行无效 | 虚拟地址 |

| c7 | 2 | 使统一Cache中某行无效 | 组号/索引 |

| c8 | 2 | 等待中断 | 0 |

| c10 | 1 | 清理数据Cache行 | 虚拟地址 |

| c10 | 2 | 清理数据Cache行 | 组号/索引 |

| c10 | 4 | 清除写缓存区 | 0 |

| c11 | 1 | 清理统一Cache行 | 虚拟地址 |

| c11 | 2 | 清理统一Cache行 | 组号/索引 |

| c13 | 1 | 预取指令Cache中的某行 | 虚拟地址 |

| c14 | 1 | 清理并使数据Cache中的某行无效 | 虚拟地址 |

| c14 | 2 | 清理并使数据Cache中的某行无效 | 组号/索引 |

| c15 | 1 | 清理并使统一Cache中的某行无效 | 虚拟地址 |

| c15 | 2 | 清理并使统一Cache中的某行无效 | 组号/索引 |

| 注意 | 编程中不能将全部Cache锁定,至少要留出一个未锁定的块来支持存储器的正常操作。 |

| 注意 | 当可执行文件加载到主存中后,在程序跳转到入口点处开始执行之前,先执行上述操作序列,以保证新加载的可执行代码正确执行。 |

| 欢迎光临 电子技术论坛_中国专业的电子工程师学习交流社区-中电网技术论坛 (http://bbs.eccn.com/) | Powered by Discuz! 7.0.0 |