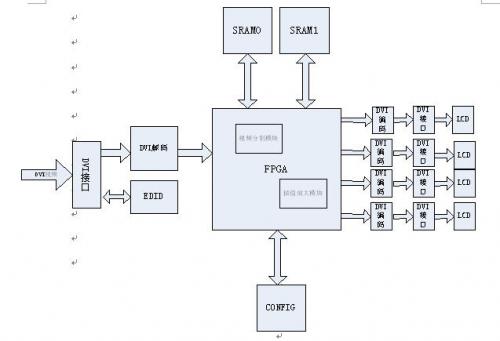

图1 LCD屏幕拼接系统结构图

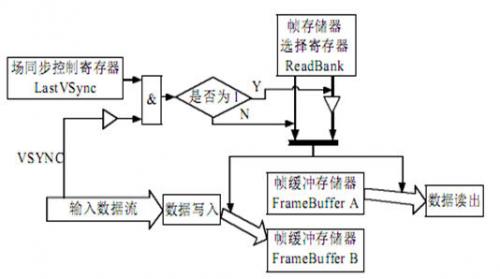

图2 SRAM读写切换示意图

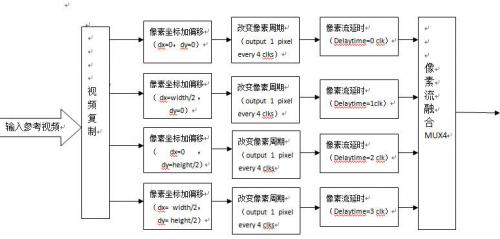

图3 插值放大模块的框图

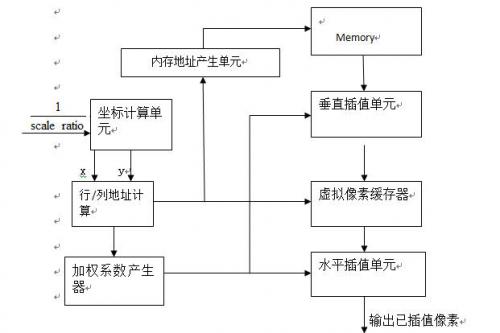

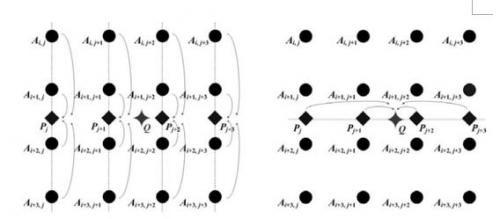

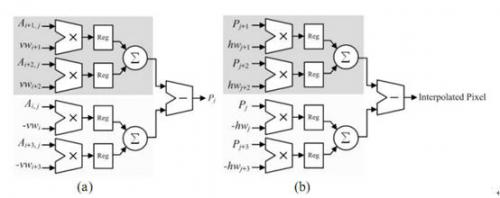

图3 水平方向与垂直方向的插值

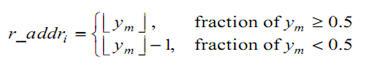

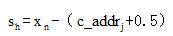

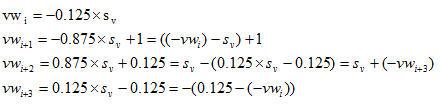

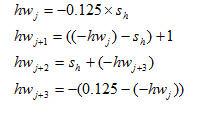

对于列或行地址计算器,输入信号决定水平与垂直方向的坐标。坐标数据包含10位的实数以及10位的小数部分。坐标数据的第9位是小数部分最重要的一位,它决定着小数部分是否大于0.5。同时由第9位控制的多路选择器控制用于输出正确的内存地址。如果输入的是列信号,那么行地址 ,

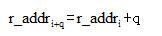

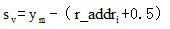

, ,

, ,

, 和垂直间隔

和垂直间隔 可由公式(1)到(3)得到,同理,列地址

可由公式(1)到(3)得到,同理,列地址 ,

, ,

, ,

, 和水平间隔

和水平间隔 能由公式(1),(2)和(4)得到。

能由公式(1),(2)和(4)得到。 (1)

(1) (2)

(2) (3)

(3) (4)

(4) ,

, ,

, ,

, ,相反的,则输出

,相反的,则输出 ,

, ,

, ,

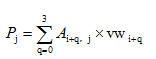

, 。在延展式线性插值最大的计算量是加权系数的计算,而最复杂的运算却由最简单的两个加法器和两个减法器构成。

。在延展式线性插值最大的计算量是加权系数的计算,而最复杂的运算却由最简单的两个加法器和两个减法器构成。 (5)

(5) (6)

(6) (7)

(7) (8)

(8)

图5水平与垂直插值单元逻辑框图

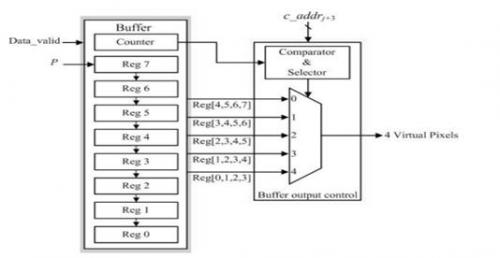

的值来决定缓存器的输出。

的值来决定缓存器的输出。

图6 虚拟像素缓存器

| 欢迎光临 电子技术论坛_中国专业的电子工程师学习交流社区-中电网技术论坛 (http://bbs.eccn.com/) | Powered by Discuz! 7.0.0 |