在通信系统中,特别是在VoIP网关、3G无线基站等系统中,随着输入语音数字和分组数据量急剧增加,系统的处理能力也需极大地增加。这需要一种功能强大的实时分布式处理系统,系统往往需要进行非常复杂的数据处理。目前使用的单个DSP已不能适应,迫切需要把多个DSP组成互连系统,以增加整体数据处理能力。在图像处理中,也需要使用多DPS系统,进行大规模的图像信号处理。本文根据TI公司DSP对外的主机接口(HPI)、外部存储器接口(EMIF)、多通道缓冲串口(McBSP),详述了利用其组成多DSP系统时各种互连方案的应用背景和优缺点。

1 TMS320C6X简介

TMS320C6X内部主要包括一个中央处理器单元CPU、一个程序内存和一个数据内存、DMA、一个外部存储器接口(EMIF)、一个主机接口(HPI)、两个多通道缓冲串口(McBSP)。TMS320C6X的CPU内部有8个处理单元,每个时钟周期最多可处理8条指令。对C6203而言,当时钟频率为300MHz时,处理能力可达2400MIPS。TMS320C6X的接口灵活、处理能力强、运算速率高,可以广泛应用于无线基站、DSL、图像处理、医疗、雷达等实时多任务处理系统中。

2 利用TMS320C5X/C6X的主机接口(HPI)组成多DSP互连系统

主机接口(HPI)是DSP是一个16/32bit宽的对外接口。外部主机可通过HPI访问DSP所有地址空间,复位时向DSP加载程序,对DSP进行控制。外部主机是HPI的主管方,DSP是HPI的从方;主机可通过HPI访问DSP,但DSP不能通过HPI向外部发起访问。

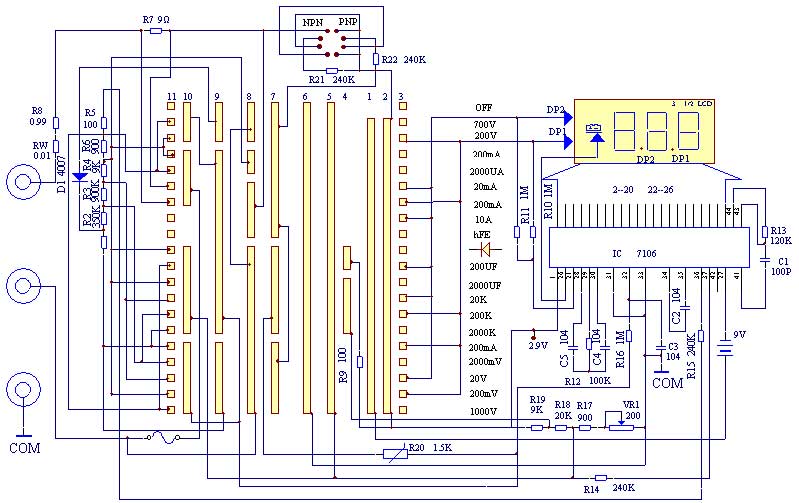

在这类系统中通常包括一个主处理器和很多从处理器。主处理器一般是通信控制处理器(如MPC8260),用来进行系统输入输出数据的协议处理并管理整个系统;从处理器一般是多个DSP(如TI的TMS320C6X),用来进行业务处理。主处理器通过HPI向DSP加载程序,对DSP进行控制;可以通过HPI向DSP写入待处理的数据或通过HPI读取DSP处理完的数据,DSP之间的数据可以通过HPI由主处理器进行中转。如图1所示,主处理器可直接连接多个DSP,HPI和主处理器之间的连接需要增加一些外部逻辑。此方案结构简单,但主处理器负担较重,和多个DSP通信效率较低,且主处理器和DSP阵列需要在同一块单板上。

另一种方案如图2所示,主处理器通过PCI总线连接到一个PCI/HPI接口转换控制芯片上,接口转换芯片控制多个DSP并完成主处理器和DSP之间、DSP相互之间的数据交换。此时主处理器和DSP阵列可以不在同一块单板上。

在该系统中(若主处理为MPC8260,需增加8260到PCI总线的桥片),HPI/PCI接口转换控制芯片是整个系统设计的关键,可选TI公司的PCI2040、PLX公司的PCI9054货源和PDF资料 href="http://www.ic37.com/stockic/P/PCI9054.htm" target=_blank>PCI9054、Tundra公司的Tsi920等。

Tsi920是一个基于PCI的多DSP端口数据传输管理芯片,是专为VoIP网关、无线基站等需要采用多DSP系统而设计的。它的一端是PCI接口,另外一端是四个HPI接口,每个HPI最多可无缝连接8个DSP。因此在一个单板系统中最多可直接管理32个DSP。DSP可以是TI公司的TMS320C5X/C6X,也可以是MOTOROLA公司的MSC8101。Tsi920的一个特点是其4个HPI端口可用时工作,使得主处理器和DSP之间通信能力提高了将近四倍;另一个特点是它具有智能的数据传输管理能力,可在DSP和主处理器之间、各个DSP之间自动传输数据,数据的传输采用特定的包路由协议进行寻址,有特定的传输数据包格式,数据包头部包含目的DSP的地址。数据的传输几乎不需要主处理器参与,使得主处理器节省了管理数据传输所需的大量时间,可以进行更为关键的协议或业务处理。

使用Tsi920构成多DSP系统的一个应用实例是VoIP网关,系统的构成如图3所示。DSP的串口通过一个TDM交换芯片(LUCENT

T8105)连接到T1/E1线上,各个DSP通过串行读入语音数据,进行多通道语音编码和回声抵消,然后把处理完的分组数据放在内部存储区;Tsi920定期查询此存储区,若发现有分组数据,则通过DSP的TPI端口取走分组数据并放入其内部FIFO,然后通过PowerSpan桥片把分组数据写入MPC8260的本地存储区;处理器(MPC8260+MPC750)对这些分组数据进行IP业务处理,并把处理完的IP数据通过MPC8260通信处理模块(CPM)的以太网接口、ATM接口或其它I/O接口送到外部网络。其中DSP阵列和主处理器可放在同一块单板上,也可放在通过PCI连接的两块单板上。

目前有一些新型的DSP本身提供了一个对外的PCI接口,如TMS320C6205、C6415、C6416,这个PCI接口和HPI接口复用。当采用这些DSP构成互连系统时,可直接通过PCI总线把多个带有PCI接口的DSP和带有PCI接口的主处理器互连起来,主处理器通过PCI总线控制各个DSP,各个DSP之间、DSP和主处理器之间可通过PCI总线传输数据。

3 利用TMS320C5X/C6X的EMIF组成多DSP互连系统

EMIF是DSP的外部存储器接品,DSP通过EMIF接外部存储器如SDRAM、SRAM、ROM等。

目前DSP的处理速度越来越高,TMS320C6203的峰值处理能力可达2400MIPS,C641X的处理能力更是高达4800~8800MIPS。然而在通过HPI连接的多DSP系统中,由于HPI为异步接口,数据传输速率有限,各个传输速率之和≤50Mbytes/s,数据传输有时会成为系统处理能力提高的瓶颈,使得CPU或系统输入输出模块产生的大量数据流无法及时送到多个DSP。在多DSP分布式处理系统中,DSP相互之间需进行大量的数据传输,然而TI的DSP没有高速的片间无缝传输机制,使得相关的任务因等待数据而被延迟,造成系统整体效率折降低。

通过EMIF可实现多DSP全互连系统。目前较实用有以下几种方案。

.共享存储器方案

共享存储器是最简单的互连方案。异步SRAM作为全局存储器由所有DSP、CPU共享,DSP访问SRAM的总线是EMIF。DSP片间通信是通过向共享SRAM中写入和读取数据两个过程完成。但EMIF访问SRAM的带宽有限,这个带宽还是多片DSP、主机分时共享。随着互连DSP数量的增加,每个DSP的平均传输带宽就要降低,总线仲裁也将变得更为复杂。

.通过FIFO直接互连方案

在多个DSP组成的全互连方案中,两两DSP之间专用的BiFIFO(双向先进先出存储器)通过EMIF接口互连,DSP各自通过BiFIFO与主机或外设互连。此方案的优点是能够实现DSP相互之间或DSP与主机之间数据的高速传输,但缺点是DSP需查询多个FIFO的状态,同时,每两个DSP固定的连接有时是不需要的,使用BiFIFO资源浪费,系统的扩展也比较困难。

.通过专用互连芯片(Crossbar)实现多DSP互连方案

可以设计一个专用互连芯片(Crossbar)来实现多个DSP、CPU、I/O器件之间的高速互连。图4所示的互连方案提供了一个按照包路由协议进行寻址交换的机制。专用互连芯片(Crossbar)提供多个异步读写FIFO接口,完成到外部器件的连接和数据包的路由转发功能。DSP通过EMIF总线访问对应端口的BiFIFO,数据由Crossbar传输到指定DSP,Crossbar同时也给主机和外部I/O模块一个通路。主机通过HPI访问和控制DSP,也可以通过Crossbar访问DSP。BiFIFO为两个芯片之间数据的突发传输提供了一个双向缓冲区。

图4中Crossbar提供6个高速互连通道,每个通道的数据总线宽度为32bit/16bit/8bit;每个通道的数据吞吐带宽可达200Mbytes/s,每个通道都提供与异步FIFO的无缝接口;Crossbar可以同时提供3对端口到端口的数据传输通道,也可以提供一端口到多个端口数据分发;任何具有FIFO接口的CPU、DSP及高速并行I/O都可以通过Corssbar及双向FIFO实现互连。

在本方案中需自定义互连路由协议,互连和路由模块(Crossbar&Router)可以由FPGA实现,每个端口上的BiFIFO当可根据实际需要选用FPGA内部逻辑实现或用专用外部器件实现。多个Crossbar进行互连可实现大规模的DSP阵列。此方案的优点是能够实现多个DSP、CPU、外部并行I/O等器件之间的数据高速转换,且扩展容易;缺点是FPGA逻辑十分复杂,实现难度较大。

下面是在3G WCDMA基站中使用Crossbar中的一个例子。在这个例子中,把上下行链路码处速率级处理和符号速率级处理、编码和译码处理主在一块单板上。码片速率级处理包括上行解扩和下行扩频,由FPGA/ASIC实现;符号速率级处理包括上行链路信道估道、信道译骊协议、下行链路信道编码协议等,由DSP实现。

系统构成如图5所示。对下行链路来说,从网络过来的数据通过UTOPIA接口进入Crossbar,然后由Crossbar中转到编码DSP,在DSP内完成信道编码协议处理,接着通过Crossbar把编码后的数据送入FPGA/ASI完成扩频,最后输出信号经过上变频并通过天线发送出去。对上行链路来说,经过射频接收和下变频后的数据首先被送入FPGA/ASIC进行码片速率级处理,如匹配滤波、解扩/解扰等,同时一片DSP辅助进行多径搜索和信道估值。在此过程中这片DSP需要和FPGA/ASIC通过Crossbar进行数据的相互传递,经过信道估值和解扩处理的数据再通过Crossbar送入另外一片DSP进行信道译码协议处理,处理结果通过Crossbar送入UTOPIA接口,接着送到基站控制器(RNC)进行处理。

4 利用TMS320C5X/C6X的McBSP组成多DSP互连系统

McBSP称为多通道缓冲串口,它有一个发送端口和一个接收端口。多个DSP可通过McBSP连接到一个串行时陈交换芯片,采用时际交换的方式进行数据交换。数据收发以帧为单位进行。每个发送帧分成n个发送时隙,不同的发送时隙对应不同的接收DSP,例如:DSP0的发送端口在时隙1给DSP1发送数据,在时隙2给DSP2发送数据,在时隙n给DSPn发送数据;每个接收帧分成n个接收时隙,不同的接收时隙对应不同的发送DSP。例如:DSP1的接收端口在时隙0来收来自DSP0的数据,在时隙2接收来自DSP2的数据,在时隙n接收来自DSPn的数据。这种方案的优点是接口简单,可以实现多个DSP的全互连,缺点是数据以串行方式传输,速率较低。

不同的应用需要的处理能力不同,对各个DSP之间、DSP与主处理器之间的数据流量和时延要求也不同,因此需要的DSP数目、互连方式也各异。利用DSP三个不同接口的互连方式,HPI有利于外部主处理器对各个DSP进行控制,适合于主处理器和多个DSP构成主从方式的互连系统;EMIF数据传输的速率高,适合于构成DSP高速全互连阵列;McBSP接口简单,适用于对传输速率要求不高的低速全互连系统;可以同时利用两种接口构成多DSP互连系统,充分利用不同接口的优点,例如可以采用HPI作为主处理器控制多个从DSP的控制接口,同时采用EMIF连接到Crossbar作为多个DSP、主处理器、外部并行I/O之间高速互连的数据接口。