|

- UID

- 871057

- 性别

- 男

|

摘要:基于SOPC技术设计了一个综合应用系统;实现了键值数据采集、显示,并将采集到的数据通过串口送给上位机;也可以接收上位机送来的数据,控制点亮相应的二极管且将接收到的数据显示在数码管上。系统硬件由FPGA及外围电路组成,采用了性能优良的Nios II软核处理器;软件在Altera公司的软件集成开发工具Nios II IDE下应用C语言编程。该系统工作可靠,在实际的应用设计中有一定的参考价值。

关键词:数据采集;控制;软核处理器;数据;工作可靠

随着IC设计与工艺水平的提高,可编程逻辑器件FPGA因其功能强大,设计灵活,开发周期短等特点,得到了越来越广泛的应用。片上可编程系统(System On Programmable Chip,SOPC)的设计方法更是越来越受到重视。SOPC将微处理器、存储器、定时器、通用I/O接口等系统设计必需的功能模块以及用户设计的特定功能的模块集成到一片可编程逻辑器件上,构成一个软、硬件可编程的片上系统。采用NiosⅡ软核处理器,使设计具有更大的灵活性。NiosⅡ系列32位RISC嵌入式处理器具有超过200DMIP的性能,在低成本FPGA中实现成本只有35美分,可以在多种系统设置组合中进行选择,满足成本和功能要求。这种设计方式使整个系统的裁减、扩充、升级变的容易,可缩短系统的开发周期,节省开发成本,延长产品的生命周期。

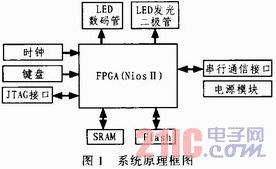

1 系统总体框图

系统一方面采集按键的键值显示在数码管上,并将键值数据通过串口送给PC;另一方面通过串口接收由PC发来的数据,将收到的数据显示在数码管上,由收到的数据控制相应的发光二极管亮。系统方框图如图1所示。

整个系统由Altera支持SOPC的CycloneII高性能、低成本、低功耗的FPGA和一些外围电路组成。采用了Nios II嵌入式处理器,在FPGA芯片上实现核心控制处理功能。外围电路主要有串行通信接口,LED数码管、发光二极管,键盘,Flash、SRAM存储器等组成2 硬件设计

利用SOPC技术结合VHDL硬件描述语言,在FPGA芯片内部设计硬件控制部分;再加上外围电路就构成了整个系统的硬件电路。FPGA内部各模块利用Altera公司提供的Quartus II开发软件和其中集成的SOPC Builder系统开发工具来设计。SOPC Builder支持Nios II CPU的配置,并支持设计者在其提供的IP库中,根据系统设计需要选择相应的接口模块,加入到NiosII系统中,将这些设计在Quartus II中编译并生成sof格式文件后,下载到FPGA芯片中就形成了SOPC的嵌入式系统硬件平台。

2.1 NiosII软核处理器

本设计选择的处理器是Altera公司推出的第二代嵌入式NiosII软核处理器。Nios II处理器系列是一种面向用户的,可以灵活定制的通用RISC(精简指令集架构)嵌入式CPU。Nios以软核的方式提供给用户,并专为在Altera的FPGA上实现作了优化,用于SOPC(片上可编程系统)集成,最后在FPGA上实现。

它的外设可以灵活选择或增删,可以自定制用户逻辑为外设,可以允许用户定制自己的指令集,使用Nios加上外部的Flash、SRAM即可构成一个嵌入式处理器系统。构建的软核处理器如图2所示。

2.2 串行通信接口

串行通信接口芯片选用MAX3232,由电平转换芯片完成从LVTTL电平到RS232C电平的转换,如图3所示。

2.3 LED数码管、发光二极管

8位数码管显示数据,通过接收的数据控制点亮相应的二极管。数码管显示译码在FPGA内部实现。发光二极管通过限流电阻直接接在FPGA的I/O口上。

2.4 Flash、SRAM存储器、键盘

系统片外FLASH选用AM29LV065DU,片外SRAM选用UM611024A;作为运行Nios II的FLASH和SRAM。十个按键KEY0-KEY9直接与FPGA芯片的I/O口连接。3 软件设计

系统的软件设计是利用Altera公司的软件集成开发工具Nios II IDE来完成,用C语言进行编程。系统的软件主流程图如图4所示。接收上位机PC发来的数据采用中断方式,中断方式能很快响应提高程序的运行效率,如图5所示。

4 结束语

本系统采用SOPC技术实现了键值采集及显示,并将数据通过串口发给上位机PC;可以接收从上位机送来的数据并显示,由接收的数据控制点亮相应的二极管。在设计中采用了Nios II软核处理器。通过实验证实了系统工作稳定,在实际的应用中具有很好的参考价值。 |

|