通过混频器,我们将多个频音组合在一起,并通过管道将这些频音输送至下一级。由于DDS内核输出是二进制补码格式,如果RF DAC需要另一种数据格式,如偏移二进制码,则需要格式转换单元。 一般来说,高性能片上BRAM通常是创建中小型用户存储系统的首选。例如,在这个平台上,我们利用赛灵思 模块存储生成器(Block Memory Generator)内核为两个频带创建两个独立的数据存储RAM。每个RAM的宽度为16位,深度为192k。

对于PC与FPGA之间的通信,我们创建了一个UART串行接口单元并将其设置为相对较低的速度,即921.6 kbps(相当于115.2字节/秒)。传输cRAM数据帧(18字节)和dRAM数据帧(约384k字节)分别需要约0.16毫秒和3.33秒时间。

器件厂商通常会以VHDL或Verilog格式提供芯片高速数据接口的实例设计。对于经验丰富的FPGA工程师而言,重利或定制参考设计并不是很难。例如,就我们系统的AD9739a和AD9129 RF DAC而言,Analog Devices公司会提供并行LVDS接口的参考设计。顺便提一下,如果无法从芯片厂商处获得实例设计,赛灵思有几款简单易用的高速接口芯片,如CPRI和JESD204B。

软件设计:MATLAB DSP功能与图像用户界面(GUI)

我们选择MATLAB作为软件主机,只是因为它在数字信号处理(DSP)性能方面具备诸多优势。另外,MATLAB还为图形用户界面(GUI)的布局提供一种称为GUIDE的简便易用的工具 。所以现在,对于这个项目,我们需要从MATLAB获得什么?

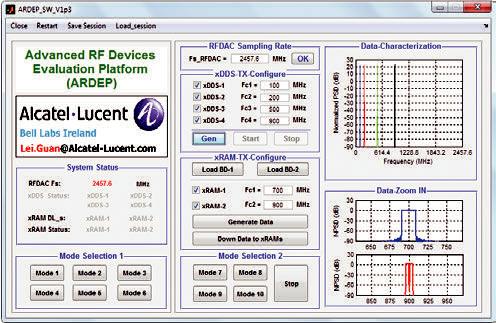

事实上,我们需要与低级DSP功能和数据流控制功能相关的用户界面。所需DSP功能为相位增量值计算器、基带数据序列发生器和数字上变频器。控制功能为数据帧封装器、UART接口控制器和系统状态指示器。

图4显示了我们为该平台创建的图像用户界面(GUI)。应首先定义RF DAC关键参数——采样率,然后才能选择xDDS模式或xRAM模式激励器件。然后,在各个子面板上,我们可以自定义参数,以调用相应MATLAB信号处理功能。在xDDS模式下,可以通过简单方程式,phase_incr = fc*2nbits/fs,计算频音fc与采样率fs的相位增量值。其中,nbits表示DDS用来综合频率的二进制位数量。按下“启动”按钮,生成的相位增量值会转化成定点格式并封装在带不同报头和控制消息的2字节数据帧内(如图3所示),然后通过UART发动至cRAM单元并在FPGA内执行。

图4 - 图形用户界面截图

在xRAM模式下,我们生成基带数据序列,将其标准化为满刻度(带符号的16位)并将其上变频为在MATLAB下所需的频率。通过UART将处理过的数据下载到dRAM之后,按下启动按钮,我们就可以调用宽频带信号测试。切记,要用FPGA侧所用相同协议参数在MATLAB配置UART串行接口。

最后,我们采用信号发生器——R&S SMU200A——来提供采样时钟,从而从逻辑上“开启”RF DAC。我们还将RF DAC输出连接至频谱分析仪,来评估频域内RF DAC的线性性能。

快速评估

在原型设计的早期阶段,关键RF组件的线性性能评估是一个关键问题,但通过我们的软硬件平台,在不影响性能的条件下可以快速进行这项评估。然后,可以添加RF功率放大器并使用所建议的平台来评估级联系统的线性。在确定非线性之后,可以执行一些数字预失真算法来消除级联系统不必要的非线性。

在FPGA设计中合理使用赛灵思 IP核可以大大缩短开发周期并提升数字系统的稳健性。展望未来,我们预计会将平台上的数据接口模块升级至JESD204B标准,以支持更高数据传输速率,从而满足多个同步RF DAC需求。同时,我们正在将FPGA主机从赛灵思 ML605迁移至Zynq®-7000全可编程SoC ZC706评估套件。Zynq SoC设计是在单台PC上创建无需任何外部DSP和控制功能的独立解决方案的一个很好的选择。 |