[导读] 本文主要针对用于ESD防护的SCR结构进行了研究。通过对其ESD泄放能力和工作机理的研究,为纳米工艺下的IC设计提供ESD保护。本文的研究主要集中在两种常见的SCR上,低触发电压SCR(LVTSCR)与二极管辅助触发SCR(DTSCR)。

关键词:防护器件电路保护ESD

摘要:本文主要针对用于ESD防护的SCR结构进行了研究。通过对其ESD泄放能力和工作机理的研究,为纳米工艺下的IC设计提供ESD保护。本文的研究主要集中在两种常见的SCR上,低触发电压SCR(LVTSCR)与二极管辅助触发SCR(DTSCR)。本文也对以上两种SCR结构进行了改进,使得其能够在不同工作环境和相应电压域下达到相应的ESD防护等级。本文的测试与分析基于传输线脉冲测试仪(TLP)与TCAD仿真进行,通过对SCR中的正反馈工作机理的阐述,证明了SCR结构是一种新颖有效的ESD防护器件。

1 引言静电放电(ESD)现象,一直是困扰集成电路设计与制造的一个难题。在整个集成电路的制造。封装。运输过程中都会产生静电,并对集成电路造成可能的损坏。每年,因ESD导致的电子产品失效所占比例从23%到72%不等。尤其是当集成电路制造进入纳米工艺(《90nm)以后,随着MOS晶体管尺寸的减小,集成电路整体的抗ESD能力愈发下降,而ESD应力本身并不会随着工艺尺寸的减小而减弱。另一方面,工作电压的降低。射频以及功率电路的特殊应用环境。IO端口的尺寸限制都对ESD防护结构提出了更高更加细化的要求。

ESD防护器件主要分为二极管。MOS管和SCR结构。其中二级管结构简单,寄生效应少,适合射频领域的ESD防护,不会给电路引入过多的寄生参数。而MOS管常采用栅接地的形式(GGNMOS),因其良好的工艺兼容性。各项ESD性能较为折中被广泛的应用于集成电路IO端口的防护之中。相比前两者,硅控整流器(SCR)结构有着最高的ESD效率。在相同的面积之下,SCR结构能够达到二极管或MOS 管结构的数倍ESD防护效果。但因为SCR的I-V曲线呈现一种深回滞的状态,容易导致ESD防护失效和闩锁效应的发生,这使得普通的SCR结构一般不能直接用于集成电路的ESD防护。需要针对不同电路的工作环境和工作电压,对SCR结构进行相应的改进设计。低触发电压SCR(LVTSCR)与二极管辅助触发SCR(DTSCR)就是两种较为成功的SCR改进结构。

2 LVTSCR结构概述LVTSCR是最早应用于ESD防护的SCR结构之一,其结构特点是SCR中内嵌了一个GGNMOS的结构(图1),带来的好处是触发电压的大幅度降低,基本能够将SCR的触发电压降低到同工艺下的GGNMOS的水平。

一个65nm工艺下的典型50um单叉指LVTSCR的TLP测试曲线如图2所示。该LVTSCR 的回滞点在6.8V,维持电压点2.6V.50um单叉指的It2能够达到2.4A.为对于图2中回滞点附近放大部分的曲线观察可以看到早在不到6V 时,LVTSCR就已经呈现开启的状态,有微弱的电流流过LVTSCR.6V左右的开启电压这与同样线宽下的GGNMOS触发电压是非常接近的,这部分电流正是在瞬态ESD条件下流过LVTSCR沟道部分的电流。

正是因为有了内嵌的栅结构,使得LVTSCR能够获得与相同工艺下GGNMOS一样的触发,实现低电压开启的目的。另外还是要注意到,尽管采用了内嵌栅实现触发电压的降低,LVTSCR的维持电压依旧是比较低的,如此低的维持电压非常容易发生闩锁效应,为此必须对LVTSCR进行提高维持电压的设计。

对于SCR结构,最为常用的提高维持电压的方法就是拉伸SCR中两个寄生三极管结构的基区宽度。

通过降低三极管的电流放大能力来减弱SCR开启后正反馈的效果,最终达到提高维持电压的目的。

图3(a)中的Dl控制的是LVTSCR的寄生NPN三极管的基区宽度。通过不断增加D1的宽度,可以获得具有高维持电压的LVTSCR结构。图4中实心部分的曲线就是采用了不同Dl的LVTSCR所获得的TLP测试曲线,可以观察到随着D1从 lure增加到4um,LVTSCR的维持电压从最低的3.2V增加到了5V.如此高的维持电压仅与触发电压有着不到2V的工作区间,避免了ESD防护失效和闩锁效应的发生。

尽管达到了提高维持电压的目的,图3(a)中的方法毕竟还是缺乏效率。因为只是在横向上增加器件的宽度,所以带来的是ESD器件整体面积的增大,这对于目前寸土寸金的IO口来说,显然是一种不能够接受的方案。为了更好地利用起硅片面积,做到有效提高维持电压的目的,本文提出了一种通过增加浮空N阱从纵向上也增加基区宽度的方法,如图3(b)所示。在拉伸后的Dl区间增加一个N阱结构,该N阱结构因为在电位上不与阳极或者阴极相连,所以其电位上是浮空的。如图3(b)中虚线部分所示,浮空N阱的加入使得基区宽度不再是横向上的一段距离,而是要加上两段N 阱的深度。在版图上,该改进结构并未增加任何的面积,是一种非常有效率的提高维持电压的方案。通过图4中空心曲线与实心曲线的对比我们可以看到:相比同样宽度的LVTSCR,增加了浮空N阱的LVTSCR的维持电压要高的多,维持电压的提高从0.3V至1v不等。

采用TCAD仿真分析,可以看到增加了浮空N阱后LVTSCR内触发电流的流向。因为在浮空N阱与 P型衬底之间会形成反型层隔绝电流经过,所以流经此处的电流必须饶果果浮空N阱的底部从阳极流向阴极,即电流路径被人为地延长了,这也是为什么增加浮空N 阱能够有效增加基区宽度,提高维持电压的原因。3 DTSCR结构概述LVTSCR能够做到相同工艺下GGNMOS相近的触发电压,但如果需要得到更低的触发电压用于极低电压电路的ESD保护,则需要改变 SCR的触发方式。通过外加辅助触发结构,SCR的开启电压是可以得到控制的。二极管辅助触发的SCR(DTSCR)就是一种更有着低电压开启特性的 SCR结构,其剖面示意图如图6所示。

这是一个外接了两个二极管的DTSCR结构,图中左边部分为主SCR,电流路径是P+/N阱/P衬底/N+.而SCR N阱中的P+/N阱以及右边独立的两个P+/N阱二极管则组成了这个DTSCR的二极管串触发电路。当ESD电流会从阳极进入,依次流过SCR中的P+ /N阱寄生二极管以及之后的两个二极管,最终由阴极流出。当流经的电流在SCR N阱中的阱电阻RNwell上形成0.7V的电压降时,DTSCR的SCR部分就会开启,成为泄放ESD的主要路径。因为二极管串的开启电压由二极管的串联个数决定,图6中3个二极管的开启电压大约是2.1V,DTSCR可以根据所应用的电压环境来调整串联二极管个数。是一种具有一定可变性的ESD防护结构。

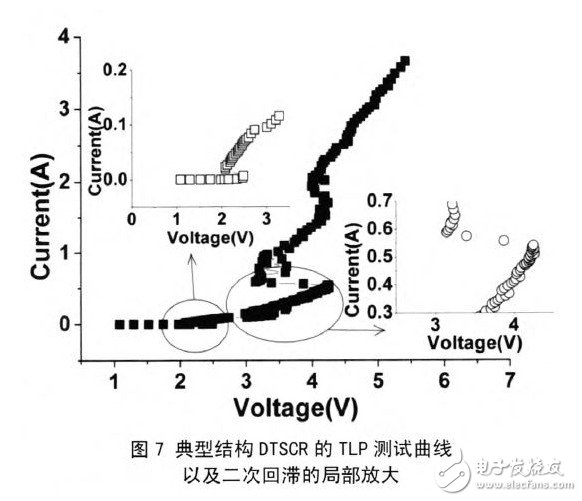

注意到图6中还标注出了寄生SCR的电流路径,该寄生SCR是由主SCR的N阱部分和最后一个二极管所构成的,正是因为该寄生结构的存在,DTSCR的TLP曲线呈现一种多次回滞的特性,如图7所示。

同样通过TCAD仿真,可以证明关于寄生SCR工作的猜想。图8中可以看到在二极管导通和主SCR开启之间,有一段寄生SCR工作的阶段,应对的正是图7中曲线一次回滞后的工作阶段。

DTSCR采用的目的是为了尽量减小整个结构的开启电压,而寄生SCR的存在则是会影响到主SCR 的开启,为了能够进一步的减小DTSCR开启电压的上限,这里依旧采用变化SCR基区宽度的方法,如图9所示,通过改变二极管串联的顺序(改为从最远离主 SCR的二极管依次串联到靠近主SCR的二极管),以及主SCR中的N阱与最后一个二极管间的N阱之间的距离D,我们可以得到图10的TLP测试曲线。可以看到随着D的变化,改进型DTSCR的第二次触发电压也发生着变化:D越小,则第二次触发电压也越低。最低可以达到3.5V的电压值。另一方面2V的维持电压值也足够用于1.2/1.8V电路的ESD防护并且能够避免闩锁效应的发生。如此一来,DTSCR真正做到了低电压触发,足够的维持电压。

4结论本文针对纳米工艺下的ESD防护特点提出使用SCR结构作为防护器件,并进行了相应的研究。

选择常见的LVTSCR结构和DTSCR,因为这两种SCR结构有着非常低的开启电压。同时也对 LVTSCR和DTSCR进行了相应的改进设计使得他们能够起到相应的ESD防护作用。通过TLP测试和TCAD仿真分析,SCR的工作原理得到了解释,测试与分析证明改进后的LVTSCR和DTSCR是有着广泛的应用前景的。

|