|

- UID

- 1023230

|

中频信号分为和差两路,高速A/D与DSP组成的数据采集系统要分别对这两路信号进行采集。对于两路数据采集电路,A/D与DSP的接口连接是一样的。两个A/D同时将和路与差路信号采样,并分别送入两个FIFO;DSP分时从两个FIFO中读出采集的数据,完成数据的采集。

1 数据采集系统组成及原理

数据采集系统由A/D、FIFO、CPLD以及数字信号处理板组成,图1为采集系统的组成框图。

系统中,和路和差路中频信号都是模拟中频信号,经过A/D 芯片将模拟信号变 成数字信号,再经过FIFO芯片,将采集到的数据送人数字信号处理板。数字信号处理板中的处理器是DSP。DSP的数据线和2片FIFO的数据线连接,同 时也和CPLD连接,地址线和CPLD连接。2片FIFO芯片的读写控制逻辑由1个CPLD进行控制。CPLD与上位机的数据线、地址线连接,数字信号处 理板通过CPLD和上位机通信。

2 芯片的特点及选择

2.1 AD6644高速模数转换器

AD6644是一种单片式的高速、高性能的14位模/数转换器,内含采样保持电路和基准源。AD6644提供兼容3.3 V CMOS电平输出;采样速率最高可达65 Msps,一般采样速率为40 Msps;信噪比典型值为74 dB,无杂散动态范围SFDR为100 dB;功耗为1.3 W,输入模拟带宽可达250 MHz,温度范围为-25℃~+85℃。

AD6644采用三级子区式的转换结构,既保证了精度又降低了功耗,其功能框图如图2所示。它的模拟信号输入方式是差分结构,每个输入的电压以2.4 V为中心,上下范围在0.55 V以内。由于两个输入的相位相差180°,所以AD6644的模拟输入信号的最大峰一峰值为2.2 V。由图2可以看出,差分模拟输入端先经过缓冲后进入第一个采样保持器(TH1)。 当编码时钟为高时,TH1进入保持状态。TH1内保持的值作为粗的5位ADC1的输入。ADC1的数字输出驱动一个5位数/模转换器DAC1。DAC1要 求具有通过激光校正的14位精度。延迟的模拟信号与DAC1的输出相减,产生第一剩余信号,并送给采样保持器TH3。采样保持器TH2的作用是延迟,为补 偿ADC1的数字延时提供了模拟延时,使送入TH3的两路信号同时到达。

第一剩余信号送人由5位ADC2,5位DAC2和通道TH4组成的第2转换阶段。第2个DAC要求具有校正的10位精度。TH5的输入是通过由DAC2输 出与被TH4延迟第1个剩余信号而获得的第2个剩余信号相减,TH4与TH2的作用相同。TH5驱动最后6位ADC3。ADC1、ADC2、ADC3的数 字输出总和与数字误差校正逻辑一起产生最终的输出数据,结果是14位二进制补码编码的并行数据。

2.2 TMS320C6713

本模块的DSP芯片选用TI公司的浮点数字信号处理器TMS320C6713。TMS320C671 3内有8个并行的处理单元,分为相同的两组。其体系结构采用超长指令字(VLIW,Very Long Instruction Word)结构,单指令长32位,8个指令组成一个指令包,总共字长为8×32=256位。芯片内部设置了专门的指令分配模块,可以将每个256位的指令 包同时分配到8个处理单元,并由8个单元同时运行。芯片的最高时钟频率达225 MHz,其最大处理能力可以达到1 800 MIPS。TMS320C6713的以上特点,保证了后端信号处理的实时性,能满足本系统的性能要求。

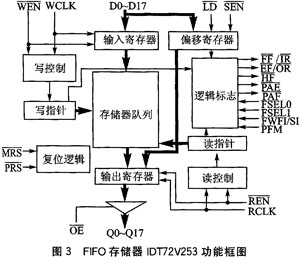

2.3 FIFO存储器IDT72V253

FIFO存储器允许数据以不同的速率写入和读出,IDT72V253是一种高速的4 096字×18位的FIFO器件,如图3所示。其最高频率可达166 MHz,数据写入数据读出时间均为10 ns。当锁入的字数超过4 096时,存储器进人满状态。FIFO的状态可通过时间和状态位——满(FF/IR)、空(EF/OR)、半满(HF)、PAE和PAF来获得。当存储器 满时,FF/IR输出为低电平;当存储器为空时,EF/OR输出为低电平。当FIFO存有不少于2 048字内容时,HF输出为高。PAE和PAF状态位是可编程状态位。当写使能端WEN电平变低时,待送入FIFO的数据在WCLK时钟的同步下送人 FIFO,当第一个字被写入时,EF/OR引脚的电平变为高电平;当送入的数据超过(n+1)(n为PAE的偏置值)个字时,可编程状态位PAE变为高电 平;当有(D/2)+1(2 049)个字写入时,HF引脚电平变低;随着数据的继续写入,会引起PAF引脚电平变低。如果没有数据读出,当有(D—m)(4 096—m)个字写入时,PAF引脚电平变低。当FIFO数据写满时(对于IDT72V253,就是写入4 096个字),FF/IR位变为低电平,阻止数据的进一步写入。当FIFO写满时,第一个读操作将会引起FF位电平变高,后来的读操作将会引起HF和 PAF引脚电平变高。当FIFO里面只有n个字时,PAE引脚电平变低;当最后一个字从FIFO读出时,EF引脚电平变低,阻止进一步的读操作。

3 高速A/D转换器与DSP的接口设计

3.1 接口设计

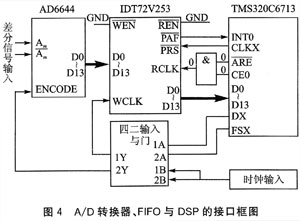

AD6644是14位模数转换器,IDT72V253是18位FIFO,TMS320C6713 DSP的数据总线是32位,所以IDT72V253和TMS320C6713只需接低14位的D0~D13。由于FIFO的先入先出特殊结构,系统中不需 要任何地址线的参与,大大简化了电路。A/D采样所得数据要实时送入FIFO,因此两者的写时钟频率必须一样,且AD6644和IDT72V253的最小 时钟输入都是10 ns,操作起来统一方便。CPLD选用Xilinx公司的xc95144xl-tql44,用它实现四二输入与门,把TMS320C6713的通用缓冲串 口(Mcbsp)中的DX、FSX配置为通用输出口(GPlO),对这个四二输入与门的通断进行控制,从而对A/D转换器和FIFO的写时钟进行控制。由 于外部FIFO占用着TMS320C6713的CE0空间,所以读信号的逻辑关系为:R=CE0+ARE,TMS320C6713的CE0和ARE相 “与”后与IDT72V253的RCLK相连,为FIFO提供读时钟(CE0和ARE相“与”由xc95144xl-tql44完成)。 TMS320C6713的CLKX与IDT72V253的复位信号PRS相连用以复位FIFO。接口框图如图4所示。

3.2 时序设计

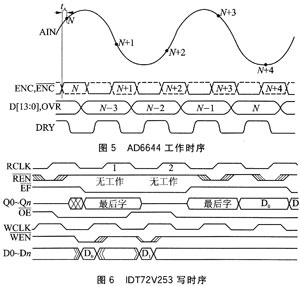

通过两个“与”门分别对A/D转换器和FIFO的写时钟进行控制,因为AD6644从模拟输入开始到该次转换的数据出现在输出口上需要4个时钟周期,并且 在高速度采样时导线的延时效果会非常明显,若把A/D转换器和FIFO的时钟连在一起,很可能过多地采到无效数据。分开控制以后,通过软件延时,可以方便 地分别对A/D转换器和FIFO的时钟进行控制,调试起来相当方便,力图把采到无效数据的位数减至最低。AD6644的工作时序如图5所 示,IDT72V253写时序如图6所示。

采样时,通过程序使DX和FSX输出为1。此时采样脉冲与DX、FSX相“与”后被分别送人AD6644的时钟输入ENCODE和IDT72V253的写 时钟输入WCLK,A/D转换器开始工作,且不断将转换数据送至自己的输出口D0~D7。当写使能WEN为低时,A/D转换器输出口上的数据在WCLK的 上升沿被依次写入FIFO。A/D转换器和FIFO每来一次脉冲,便完成一次模数转换并把数据顺序存人FIF。使IDT72V253的LD为低、 FSELO为高、FSEL1为高时,IDT72V253经过主复位后,偏移值n、m为默认值63,每个雷达回波脉冲采样63个点后,存储器几乎满标志 PAF输出低电平(在未到63时输出高电平)。把此标示接到TMS320C6713的外部中断INT0上,利用它由高到低的变化产生中断,以表明一组数据 采集完成。

在中断中,DSP首先迅速关闭采样脉冲信号(使DX和FSX的输出为0),停止A/D转换器和F1FO的工作。TMS320C6713的CE0和ARE相 “与”后与FIFO的读输入RCLK接在一起,DSP每执行一次I/O读操作,R=CE0十ARE便向RCLK发出一脉冲,把FIFO读使能PEN置为 低,同时连续执行63次I/O读操作,数据便依次从IDT72V253送入TMS320C6713,整个数据采集工作就此完成。在进行第二次数据的采集 前,最好将IDT72V253先复位,把TMS320C6713通用缓冲串口的CLKX配置为通用输出口,给IDT72V253的PRS引脚输入一个不小 于10 ns的低脉冲,即在DSP的CLKX引脚输出一个低脉冲。这样可以更充分地保证FIFO的读、写指针的稳定。

3.3 软件设计

软件设计包括CPLD和DSP两个部分。CPLD程序用VHDL语言编写,实现简单的逻辑转换功能,程序设计比较简单。DSP编程中有几个关键步骤:外部 中断使能、时钟送入A/D转换器和FIFO、等待中断、停止A/D转换器和FIFO、采集数据、复位FIFO。整个软件流程如图7所示。

4 结 论

通过实际设计表明,在DSP高速数据采集系统中,采用FIFO器件作为A/D转换器与DSP之间的桥梁,可以根据具体需要灵活设置FIFO的各个标志,使 其具有很强的外部接口能力;并且通过软件很容易调整A/D转换器、FIFO和DSP的操作时序,增强了操作的灵活性,起到了很好的数据缓冲作用,保证了数 据采集的安全可靠。系统硬件具有结构简单、性能可靠的特点;软件具有控制灵活、程序调试方便等优点。 |

|