【晒FRAM铁电存储器样片】+接下来的项目使用构想

|

- UID

- 531326

- 性别

- 男

|

【晒FRAM铁电存储器样片】+接下来的项目使用构想

本帖最后由 youzizhile 于 2014-7-16 22:56 编辑

在一个项目中,想要实时记录当前的系统中相关开关位置的操作和指示灯的状态处理,所以想找一个高可靠性和实时性的器件来存储数据,数据量不大,但是要求快速可靠。原来想选择E2PROM,但现在富士通的MB85RS64铁电存储器不仅速度可以满足要求,而且性能和可靠性都可以满足,功耗又特别的低,可靠性应该比E2PROM要高很多,所以在项目中,会优先考虑这款芯片的! |

|

|

|

|

|

|

- UID

- 531326

- 性别

- 男

|

本帖最后由 youzizhile 于 2014-8-21 11:05 编辑

本来是要和另外一个新项目使用后在发布的,但是现在由于另外一个新项目的计划拖延,导致不能按时完成,所以想用另外一种方式来体验下这个芯片的性能,为以后的设计做充足的准备。

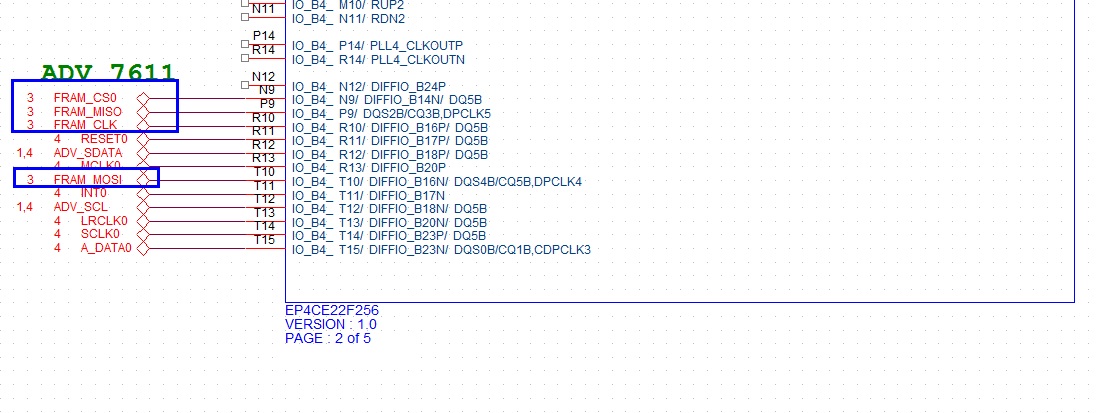

这是之前应用了一个项目,是关于FPGA进行HDMI视频芯片ADV7611配置的应用。使用了非易失的EEPROM来作为存储芯片。现在手中有了富士通的 FRAM , 现在把电路更改为MB85RS64,要在试用下。

下面是cadence的设计电路截图:

下图中的蓝色标注部分为FPGA与fram连接管脚:

|

|

|

|

|

|

|

- UID

- 531326

- 性别

- 男

|

module MB85RS64_SPI_CONTROLLER(

clk,rst_n,

miso,mosi,sck,

tx_en,tx_rdy,rx_en,rx_rdy,tx_db,rx_db

);

input clk; //FPAG输入时钟信号

input rst_n; //输入复位信号

input miso; //SPI信号

output mosi; //SPI信号

output sck; //SPI时钟信号

input tx_en; //SPI数据发送使能信号,高有效

output tx_rdy; //SPI数据发送完成标志位,高有效

input rx_en; //SPI数据接收使能信号,高有效

output rx_rdy; //SPI数据接收完成标志位,高有效

input [7:0]tx_db; //SPI数据发送寄存器

output [7:0]rx_db; //SPI数据接收寄存器

//模拟SPI的时序模式为CPOL=1, CPHA=1

//------------------------------------------------------

//SPI时序控制计数器,所有SPI时序由该计数器值控制

reg [4:0]cnt; //SPI时序控制计数器,计数范围在0-18

always @(posedge clk or negedge rst_n)

if(!rst_n)

cnt <= 5'd0;

else if(tx_en || rx_en)

begin //SPI工作使能

if(cnt < 5'd18)

cnt <= cnt + 1'b1; //计数到18停止,等待撤销spi使能

else

cnt <= 5'd0; //SPI关闭,计数停止

end

//--------------------------------------------------------

//SPI时钟信号产生

reg sckr; //SPI时钟信号,由主机产生

always @(posedge clk or negedge rst_n)

if(!rst_n)

sckr <= 1'b1; //spi时钟只有在spi启用过程中才有效

else if(cnt >5'd1 && cnt <5'd18)

sckr <= ~sckr;//在cnt8处于2-17时SPI时钟有效翻转

assign sck= sckr;

//-------------------------------------------------------

//SPI主机输出数据控制

reg mosir; //SPI主机输出从机输入数据信号

always @(posedge clk or negedge rst_n)

if(!rst_n)

mosir<= 1'b1;

else if(tx_en)

begin

case(cnt8[4:1])

4'd1: mosir <= tx_db[7];

4'd2: mosir <= tx_db[6];

4'd3: mosir <= tx_db[5];

4'd4: mosir <= tx_db[4];

4'd5: mosir <= tx_db[3];

4'd6: mosir <= tx_db[2];

4'd7: mosir <= tx_db[1];

4'd8: mosir <= tx_db[0];

default: mosir <= 1'b1; //mosi没有输出时应保持高电平

endcase

end

else

mosir <= 1'b1; //mosi没有输出时应保持高电平

assign mosi = mosir;

//---------------------------------------------------------------

//SPI主机输入数据控制

reg [7:0]rx_dbr; //SPI主机输入从机输出数据总线寄存器

always @(posedge clk or negedge rst_n)

if(!rst_n)

rx_dbr <= 8'hff;

else if(rx_en) begin

case(cnt)

5'd3 : rx_dbr[7] <= miso;

5'd5 : rx_dbr[6] <= miso;

5'd7 : rx_dbr[5] <= miso;

5'd9 : rx_dbr[4] <= miso;

5'd11: rx_dbr[3] <= miso;

5'd13: rx_dbr[2] <= miso;

5'd15: rx_dbr[1] <= miso;

5'd17: rx_dbr[0] <= miso;

default: ;

endcase

end

assign rx_db = rx_dbr;

//-----------------------------------------------------------------

//SPI数据发送完成标志位,高有效

assign tx_rdy = (cnt == 5'd18);

//------------------------------------------------------------------

//SPI数据接收完成标志位,高有效

assign rx_rdy = (cnt == 5'd18);

endmodule |

|

|

|

|

|