基于FPGA+ARM的HDLC协议控制器的设计与实现(2)

|

- UID

- 1029342

- 性别

- 男

|

基于FPGA+ARM的HDLC协议控制器的设计与实现(2)

2.3 HDLC数据处理单元

HDLC数据处理单元主要完成信息的帧的CRC校验和打包解包任务,其处理芯片采用意法半导体的STM32F103系列ARM芯片,该芯片具有开发简单灵活,成本较低的优势。数据处理单元对数据的处理同样包括接收和发送两部分,以接收为例,具体工作流程图如图5所示。

当进入接收中断进程时,首先读空接收FIFO,其中最后两次读出的数据为该帧信息的CRC校验码,利用该校验码进行CRC校验,校验采用CRC-16-CCITT标准,生成r取值为16,其生成多项式为:C(x)=x16+x12+x2+1传统CRC校验是对消息逐位处理,对于ARM来说,这样效率是很低的。为了提高时间效率,通常的思想是以空间换时间。考虑到内循环只与当前的消息字节和crc_reg的低字节有关,针对crc_reg低字节建立数表进行查询相应的CRC校验码,最终循环完毕如果没有差错发生则结果应为0.

发送单元与接收单元类似,为其逆过程,首先将信息按约定帧格式打包,然后进行CRC校验,将校验码放入信息帧的最后2个字节,并将该信息帧通过数据总线存入FPGA的发送FIFO中,最后写入发送标志字,启动FPGA发送传输控制逻辑。

3验证及结果

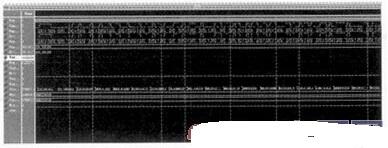

为完成设计,首先采用ModelSim进行仿真验证,如图6所示通过激励文件生成ARM与FPCA的读写时序,给出符合HDLC帧格式的一组数据写入FPGA发送FIFO,并启动发送,在激励文件中将RX/RCLK与TX/TCLK短接,形成回环,FPGA根据协议控制器接收到数据,并将数据存入接收FIFO,完成验证。其逻辑时序满足HDLC协议帧格式和通信时序要求。

图6 HDLC协议控制器ModelSim仿真验证图

最后按照设计要求将设计好的HDLC通信协议控制器加载至FPGA与ARM上,并与串口通信卡BST23109进行回环测试,该卡能够实现串口同步模式,通信满足HDLC协议要求。试验结果表明在5 m通信距离内,波特率可达2 Mb/s,误码率为10-8.

4结论

文中针对飞行模拟装置中HDLC协议的应用需求开展了HDLC协议控制器的设计,文中首先介绍了HDLC协议的相关内容,然后重点介绍了HDLC协议控制器软硬件实现,详细给出于HDLC协议控制器的没计实现过程。通过仿真和实测试验表明在5m通信距离内,波特率可达2Mb/s,误码率为10-8.在该飞行模拟装置交付使用过程中,该控制器功能完整,能够很好地满足各项指标的技术要求。 |

|

|

|

|

|