心率计是常用的医学检查设备,实时准确的心率测量在病人监控、临床治疗及体育竞赛等方面都有着广泛的应用。心率测量包括瞬时心率测量和平均心率测量。瞬时心率不仅能够反映心率的快慢。同时能反映心率是否匀齐;平均心率虽只能反映心率的快慢,但记录方便,因此这两个参数在测量时都是必要的。

测量心率有模拟和数字两种方法。模拟方法是在给定的时间间隔内计算R波(或脉搏波)的脉冲个数,然后将脉冲计数乘以一个适当的常数测量心率的。这种方法的缺点是测量误差较大、元件参数调试困难、可靠性差。数字方法是先测量相邻R波之间的时间,再将这个时间转换为每分钟的心跳数测量心率的。这种方法的优点是测量精度高、可靠性好,并且能同时测量瞬时心率和平均心率。用数字方法测量心率的电路又分为两种类型:一种是使用一个可预置的计数器实现现除法电路;另一种是通过自动下降的时钟频率测量相邻R波之间的时间。

本心率计在数字式心率计的基础上,采用FPGA和VHDL语言实现,减少了元器件使用数量,提高了测量精度和可靠性。该电路能够实时采集并测量人体心跳的瞬时和平均心跳速率,判断并显示心率状态(即心跳是否正常、是否过快或过慢、是否有心率不齐现象)。如果心率过快或过慢或者有心率不齐现象,那么将用不同颜色发光管进行闪烁报警显示。

1 测量方法及电路组成

1.1 测试方法

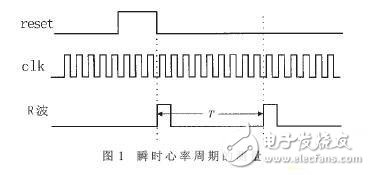

如上所述,采用数字方法测量瞬时心率(Intantaneous Heart Rate,IHR)时,先测量两相邻R波之间的时间(即心率周期),再将这个心率周期转换为每分钟的心跳数。如图1所示,设心率周期为T秒,则瞬时心率的计算公式为IHR=60/T。如果用频率为f0的时钟脉冲作为测量时间基准,在T秒时间内对时钟脉冲计烽,并设计数值为N,则T=N/f0秒,故瞬时心率的计算公式为IHR=60f0/N。当f0=1kHz时,IHR=60×1000/N=60000/N。

平均心率(Average Heart Rate)的测量是将一定时间内测得的各个瞬时心率求平均值。设测得的瞬时心率为IHR1,IHR2,…,IHRn,则平均心率的计算公式为:

AHR=(IHR1+IHR2+…+IHRn)/n

1.2 电路组成

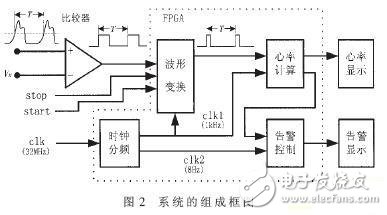

系统的组成框图如图2所示。按下start开关将启动测量过程,由传感器获得的模拟心电信号(R波或脉搏波)经过放大后加到比较器的一个输入端,与另一个输入端的参考电压进行比较,将心电信号转换为同周期的方波信号,再输入FPGA进行心率测量。

在FPGA中,波形变换电路首先将这个脉冲宽较宽的方波信号进行微分,转换为脉冲宽度等于时钟信号(clk1)一个周期的方波信号,通过周期计数器在心率周期T时间内对时钟信号计数,再根据前面给出的瞬时心率计算公式做除法运算即可得到瞬时心率。瞬时心率通过译码电路转换为七段显示代码后送到 FPGA外部的三个LED显示器上进行显示。在一次测量结束时,心率计算模块将测到的各个瞬时心率求平均,得到的平均心率转换为七段显示代码也送到三个 LED显示器进行显示。

告警控制模块根据每一个瞬时心率值判断心率是否正常、是否过快或过慢,并根据相邻两个瞬时心率值判断是否有心率不齐现象,分别以英文字母E(正常)、F或S(过快或过慢)及I(心率不齐)的七段显示代码送告警显示电路中的三个LED显示器进行显示,并将这三种心率状态以8Hz的频率送到告警显示电路中颜色分别为绿、红、黄的三个发光二极管进行闪烁报警显示。按下stop开关将结束测量过程,并将平均心率送三个LED显示器进行显示。

系统的主时钟频率为32MHz,送到FPGA中的时钟分频电路产生1kHz和8Hz的时钟频率,分别送到用作波形变换、瞬时心率计算和心率状态显示的波形变换模块、心率计算模块和告警控制模块。系统中的数字电路全部由FPGA芯片实现,外围只有少量的模拟器件,包括比较器、LED和发光二极管显示器、电源电路及晶振电路等,因而系统的体积小、工作稳定、可靠性高。

2 FPGA中各模块的电路组成及工作原理

2.1 波形变换电路

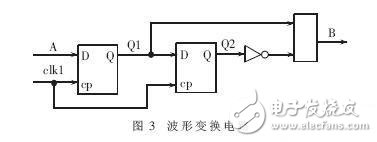

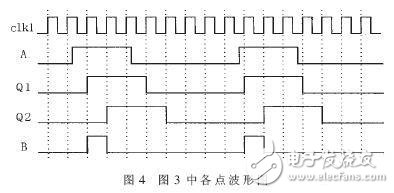

由比较器获得的方波心率脉冲还不能直接用于心率测量,因为脉冲宽度太大。要进行正确的心率测量,必须对这个方波脉冲进行微分,将其宽度调整为一个时钟周期宽。微分电路如图3所示。用VHDL语言编程时,可用一个时钟进程实现这个微分电路。图3中各点波形如图4所示。

2.2 心率计算电路

根据瞬时心率计算公式及图1,瞬时心率的计算应以1kHz的时钟频率作为时间基准,测量相邻两次心跳之间的时间,然后做除法运算。因此,瞬时心率计算电路应包括一个12位的二进制计数器和一个16位的二进制除法电路。平均心率的计算应根据测量结束前最后测得的16次心率值求平均,因此心率计算电路还应包括一个能完成12位二时制数加法的电路和一个能完成12位二进制数除法的电路,这个除法运算可通过移位寄存器右移四次来实现。计数器、加法器和移位寄存器在FPGA中用VHDL语言实现都很容易。下面主要讨论测量的实现方法。

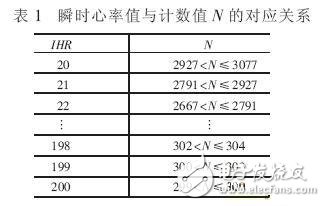

瞬时心率计算公式是一个抛物线函数,分母中计数值N是一个变量,这个除法运算不能通过简单的移位寄存器来实现;而设计16位二进制除法运算电路,无论采用组合电路还是采用时序电路,都将耗费很多的芯片资源。另一方面,人的正常心率为60~120跳/分钟,即使心率出现异常,也不会超过 20~200跳/分钟,因此所测量的心率值只有有限个数据。这样,可根据每一个可能出现的心率值,预先求出N的变化范围,制作一张表,存入ROM中。实际测量时,再根据测到的N值,选择相应的心率数据。假设心率的变化范围为20~200,则N的变化范围为3077~300。瞬时心率值IHR与计数值N的关系如表1所示。

心率计算电路除了完成上述功能外,还要将瞬时心率值和平均心率值转换为七段显示代码,再送入LED显示器进行数字显示。

2.3 告警控制电路

告警控制电路的功能是根据心率计算电路得到的瞬时心率值来判断心率的状态:心跳到否正常、是否过快或过慢、是否心率不齐。如果心率处于 60~120的范围,则心跳正常;如果心率小于60,则心跳过慢,如果心跳大于120,则心跳过快;如果相邻两次测量的心率值认为心率不齐。这些判断是由一系列比较器完成的,用VHDL语言实现比较简单,这里不再详述。

完成比较判断后,告警控制电路将代表不同心率状态的字母E(正常)、F或S(过快或过慢)及I(心率不齐)的七段显示代码以8Hz的频率分别送到三个LED显示器进行报警显示,同时将不同心率状态信号以8Hz的频率分别送到三个不同颜色的发光二极管进行报警显示。

2.4 时钟分频电路

时钟分频电路的功能是将系统提供的主时钟进行分频,提供其它模块电路所需的两个时钟(1kHz和8kHz)。其中,周期计数器的时钟(clk1)决定了周期计数器的位数。当心率测量范围为20~200跳/分钟时,对庆的心率周期T为3~0.3秒。若时钟信号clk1的频率 f0=1kHz,则在最低心率(20跳/分钟)时的计数值N=3/10 -3=3000,因此计数器的位数为12位。由下面的性能评价佛标分析可知,更高的时钟频率可扩大心率测量范围并提高测量分辨率,但同时分增加电路的复杂性;而报警控制电路的时钟(clk2)决定了显示闪烁的快慢。在FPGA中,时钟分频电路一般是通过VHDL语言的进程语句由计数器实现的。

3 性能评价指标

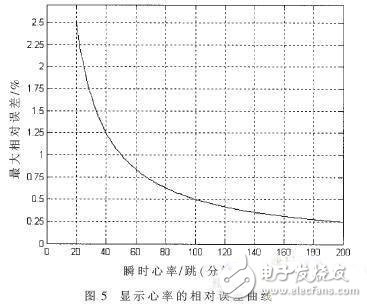

心率计数能评价指标主要包括测量误差和分辨率。由表1可知,由于计数值N的边办取值对应于相邻两个心率值的中点,故在20~200跳/分钟范围内测量的每一个显示心率值的误差都为0.5跳/分钟。最大相对误差(用百分比表示)如图5所示。相对误差的最大值发生在最低心率20跳/分钟处,随着心率值的增加,相对误差减小。当心率值大于或等于50跳/分钟时,相对误差小于1%,而当心率值大于100跳/分钟时,相对误差小于0.5%。

另一个性能指标是仪器的分辨率。由瞬时心率IHR=6×10 4/N和表1可知,当周期计数值N较小时,N变化一个单位(增大或减小1)对应瞬时心率变化比较大。因此,高心率处的分辨率较差,而低心率处的分辨率较好。在瞬时心率接近200跳/分钟时,N值很小,分辨率为1跳/分钟;在较低的瞬时心率时,分辨率小于1跳/分钟。

如果将时钟频率提高到8kHz,同时将周期计数器的位数提高到16位,分辨率将会大幅提高。此时,在瞬时心率接近200跳/分钟处,分辨率会小于0.1跳/分钟,而在瞬时心率较低处,分辨率将进一步变好。因此,在20~200跳/分钟的心率范围内,可以0.1跳/分钟的分辨率显示所有心率。不过,将周期计数器从12位提高到16位会增加电路的复杂性。另外,在实际心率测量中,人们习惯1跳/分钟的分辨率,更高的分辨率没有必要。

基于FPGA的数字心率计测量精度高,测量范围宽,在20~200跳/分钟的测试范围内,最大误差为2.5%,而当心率大于50跳/分钟时,误差小于1%,而且它的工作稳定性和可靠性好、功耗低、不需要电路参数校正和灵敏度调节,能够测量瞬时心率和平均心率,并具有心率异常报警功能。因此,与文献中报道的其它心率计相比,具有更好的性能。

|