|

- UID

- 1023230

|

针对目前广泛对高精度频率源的需求,利用FPGA设计一种恒温晶振频率校准系统。系统以GPS接收机提供的秒脉冲信号为基准源,通过结合高精度恒温晶振短期稳定度高与GPS长期稳定特性好、跟踪保持特性强的优点,设计数字锁相环调控恒温晶振的频率。详细阐述系统的设计原理及方法,测试结果表明,恒温晶振的频率可快速被校准到10 MHz,频率偏差小于0.01Hz,具有良好的长期稳定性,适合在多领域中作为时间频率的标准。

时钟技术在现代科学技术中有着广泛的应用,许多领域对时间指标的要求越来越高,如电力、通讯、军事、航空航天等,都需要高精度的同步时钟作为参考,协调整个系统的正常运行。GPS是目前世界上应用范围最广、实用性最强的全球精密授时、测距和导航定位系统。高精度频标目前主要有铷钟、铯钟、氢钟等原子钟以及高精度晶体振荡器。其中,高精度晶体振荡器以其使用寿命长、价格较为便宜等优点,获得了广泛应用,但是晶体振荡器会由于温度、老化等因素产生频率的漂移,长期稳定性较差。为了获得一个短期及长期稳定度都比较优良的时间频率标准,本系统以授时型GPS秒信号为参考,通过数字锁相环对高稳晶振的频率进行控制与修正,此方法具有便携、廉价等优势。

1 GPS接收机测试及恒温晶振选型

1.1 GPS接收机测试

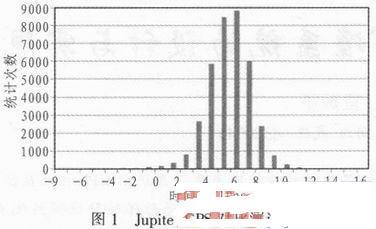

系统选用并行12通道,正常接收卫星时,秒脉冲(1PPS)时间精度优于100 ns,并且输出与秒脉冲完全同步的10 kHz信号的Jupiter授时型GPS接收机。由于天线角度、电离层、对流层、多径效应、接收机自身特性的影响,GPS会产生失锁或者虽然锁定但秒信号抖动较大,此时测得的时差数据有很大的噪声分量。在同一地点,当两台Jupiter授时型GPS接收机都正常接收卫星时,连续10小时以一台GPS的1PPS作为基准,对比另一台GPS的1PPS到达时刻,绘出到达时间差的柱状统计图,从图1中可得出,两台GPS接收机正常运行时,两个1PIPS信号的时间差99%以上集中在0~100 ns之间,时间差的均值是54 ns,主要是由GPS天线引起;计算出均方差为7.64 ns,可以看出两台Jupiter GPS接收机的1PPS信号一致性很高,抖动较小。但是对于随机误差引起的1PPS跳变或者GPS接收机偶然锁星失败,虽然也输出1PPS信号,但其精度较低不能作为基准源。

1.2恒温晶振选型

GPS接收机输出的1PPS信号存在较大的随机误差,但是没有累计误差,而恒温晶振时钟信号的随机误差较小,不过由于自身老化和外界温度等一些因素的影响,存在频率漂移现象,具有较大的累计误差。如果恒温晶振长期不问断的运行,频率无法满足工作所需的准确度与稳定度,因此需要通过实时的自动调控压控端电压来进行频率校准。根据卫星时钟信号和恒温晶振时钟信号精度互补这一特点,通过调控恒温晶振的压控端,使其输出频率随之改变,以维持短期和长期的时间精度和稳定性。

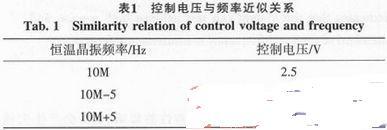

恒温晶振选用俄罗斯莫里恩(Motion)公司的低漂移、低相噪薄型双恒温槽超精密恒温晶体振荡器OCXO MV180.该恒温晶振输出标准频率为10 MHz的正弦波,短期稳定度小于2x10-12/秒,年老化率为±1×10-8/年,对周围环境变化敏感度低,长期温度-频率稳定度可达±1×10-10,还提供了一个直流电压控制端。通过向压控端施加一个0~+5 V的直流电压,可使该恒温晶振有±5 Hz左右的频率调整范围,控制电压与晶振频率的近似关系如表1所示。

2系统设计

系统以FPGA作为控制器,芯片选用Altera公司的EP3C25E144C8,内部具有丰富的逻辑资源。开发平台是Quartus II集成开发环境,采用Vetilog HDL语言对各功能模块进行逻辑描述,并完成了逻辑编译、逻辑化简、综合及优化、逻辑布局布线,并使用Modelsim、Signalnap II进行逻辑仿真,实现系统的设计要求,系统的原理框图如图2所示。

2.1数字锁相环

恒温晶振的频率调整功能是靠数字锁相环(DPLL)实现的,同模拟锁相环类似,它属于闭环的控制系统,由鉴相器(PD)、环路滤波器(LPF)、D/A转换器、压控恒温晶振(OCXO)组成。系统启动后,在FPGA内部,数字鉴相器模块首先以GPS接收机输出的10 kHz时钟信号作为基准源,对恒温晶振整形并经过分频后的10 kHz信号进行快速鉴相,用恒温晶振倍频后的300 MHz时钟对相位差进行量化,得到具体的超前或滞后数据,进而传递给环路滤波器模块,设置抖动门限参数,若相位超前或滞后量达到门限值,则迅速通过D/A转换器,对晶振的压控端电压进行相应调节。此方法可令晶振频率快速接近10 MHz,但是恒温晶振频率的改变需有一定的响应时间,快速调整压控端的电压会产生过调现象,频率稳定度不佳。

为进一步提高晶振频率的精度与稳定性,结合恒温晶振短期稳定度高的特点,在数字鉴相器模块中,以GPS的1PPS信号为基准,测量1PPS与恒温晶振分频出的1Hz信号的相位差。依据GPS没有累积误差的优点,在环路滤波器模块中采用滑动平均滤波法来降低GPS秒脉冲对测量带来的干扰,设计FIFO存储器来配合计算出最近200 s的平均相位差,通过不断对比短时的相位差及长时的平均相位差,分析相位差的长期与短期变化动态,实时调节恒温晶振的控制电压,保证晶振输出稳定且准确的10 MHz时钟信号。晶振频率调整的过程如图3所示,此方法简单实用,可有效抑制1PPS抖动对晶振造成的影响。

2.2电路设计

D/A芯片选用TI公司TLV5616,它是低功耗单片12位串行数模转换器,分辨率为4096,该芯片采用三线制(SCLK、SYNC、DIN)串行接口,SCLK方波信号为下降沿时,TLV5616读取DIN的电平信号,转化成相应的电压送往恒温晶振,用于晶振的微调,晶振频率调整硬件电路如图4所示。

2.3授时功能

在许多现实的应用中需要毫秒、微秒、纳秒等这些更小的时间单位量,但是GPS接收机一般只能提供最小时间单位为秒的UTC时间,本系统在GPS基础上设计了授时功能。

授时工作流程如图5所示,系统在FPGA中设计串口数据模块来接收GPs的SD01管脚发出的GPRMC格式数据,并将其存放在FPGA内部的双口RAM中,通过串口数据模块及数字鉴相器模块可以判断GPS接收机是否正常工作。若识别出准确的UTC时间和1PPS信号后,授时模块迅速从RAM中提取最新时间数据进行处理,得到初始时间值,当下一个1PPS上升沿到来后,系统在初值的基础上开始完全依靠高稳恒温晶振自行走时,并每隔5秒与准确的1PPS信号进行校对,如果发现本系统的时间与1PPS不同步,那么系统时间将会短暂停滞或快速跳进,达到与1PPS同步,保证时间信息输出的连续性与准确性;若GPS接收机非正常输出1PPS信号,则不进行校对,直到1PPS正常后再恢复校对功能。 |

|