摘要:

随着嵌入式领域和信息时代的蓬勃发展,微处理器设计开始被越来越多的人关注。目前国内很多高校和研究机构都开始设计微处理器。客观的讲,这些微处理器在硬件结构上比较简单,缺乏汇编器、编译器、操作系统以及各种I/O接口电路的支持,应用场合单一。另外,由于这些微处理器支持的指令集在格式上各有不同,因此造成了大量的设计资源浪费。我们旨在设计一套完备的高性能嵌入式SoC(System on Chip)系统,用以减少重复性设计工作,更好地普及高等院校的微处理器设计教育,吸引更多的人才专注于高性能微处理器研发;同时也提供给企业免费的SoC软核,用于低成本的工业控制。

关键词:RISC,微处理器,片上系统,minisys

1. 系统原理和技术特点

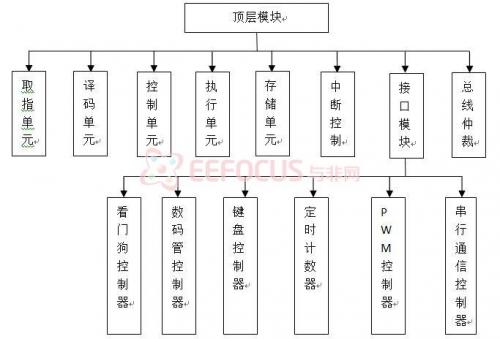

Minisys是东南大学计算机科学与工程学院系统结构实验室开发的一款基于32位RISC架构的SoC系统。如图1所示,Minisys包含一个以32位RISC型处理器为核心,附带多个IO控制器的SoC芯片和相关的系统软件。系统软件包括以便于上层软件编程而提供的系统功能调用接口为主体的BIOS、键盘驱动程序、以及Minisys汇编器(编译器)。其中,Minisys SoC芯片功能结构如图2所示。

图1 Minisys系统结构图、

图2 Minisys芯片功能结构图

Minisys CPU有32个32位通用寄存器,32位数据线和16位地址线。IO部件包括一个4位7段LED数码管控制器,一个4×4键盘控制器,一个16位定时/计数器,一个32位系统定时器,一个16位PWM控制器,一个看门狗电路和一个简易UART串行通信控制器。

Minisys借鉴了MIPS指令集,指令定长32位,共有31条常用定点指令(不包括硬件乘除、硬件浮点指令)。32个32位寄存器除了5个寄存器被固定功能外,其余的都可以做通用寄存器。

Minisys采用哈佛存储结构,片内包含4KB ROM和4KB RAM,都采用字节编制,但以32位为一个存储单元,即他们和CPU之间的数据交换都以32位为单位进行。Minisys的I/O空间编址采用与存储器统一编址方式,即将整个地址空间分为两个部分,一部分作为访问RAM的存储空间,另一部分作为访问IO的I/O空间。因此,对I/O部件的访问采用与存储器访问相同的指令格式。

系统内部提供两个中断源的控制电路,两个中断源为INT0和INT1,其中INT0的优先级高于INT1,允许高优先级中断嵌套。系统提供用于堆栈操作的SP寄存器,但没有提供压栈和退栈指令,因此对于堆栈的操作需要用软件实现。堆栈操作的原子性由程序员负责。

2. 系统设计流程

Minisys SoC的设计包括了硬件设计和软件设计。其中,硬件设计部分包括以下几个部分:Minisys CPU的设计、接口部件的设计、BIOS的设计。软件设计即为汇编器的设计。

在Minisys CPU设计中,主要考虑指令系统的确定、CPU结构的设计与实现、CPU寄存器组的组织与实现以及CPU的各个功能部件的设计与实现。下面主要介绍Minisys CPU的各个功能部件的设计和实现。

Minisysy CPU的内部功能部件被划分为5歌基本单元:取指单元、译码单元、控制单元、执行单元和存储单元。在设计CPU的时候,采用模块化的设计方法,因此,以上这些单元是分别在相应的5歌模块中进行设计,最后用一个顶层模块将这5个模块按照逻辑上的需要连接起来,成为一个完整的CPU。

取指单元主要完成以下工作:到程序ROM中取指令;对PC值进行更新;完成各种跳转指令的PC修改功能。本设计是在Altera公司的Quartus II环境下完成的,因此,在设计中使用了Altera公司已经设计好的rom宏模块。

译码单元的主要工作就是完成执行指令前的操作数准备工作,分析Minisys指令集得知,这些数据或者在寄存器中,或者是立即数,因此在译码单元中最重要的工作就是实现寄存器组和完成寄存器的读写并根据指令译码结果,决定向其他部件送一路还是两路数据。

控制单元是整个CPU的控制核心,各种控制信号都是从这里发出来的,而各种信号的值都是通过操作码和功能码的不同组合和一些约定来决定的。在设计中用SRCB来标志操作数的来源,具体操作如表1和表2所示。

表1 操作数A的来源标志 操作数 | 零扩展的立即数 | ID阶段取得的寄存器值 | SRCA | 1’b0 | 1’b1 |

表2 操作数B的来源标志

操作数 | ID阶段取得的寄存器值 | 符号扩展的立即数 | 零扩展的立即数 | SRCB | 2’b00 | 2’b01 | 2’b10||2’b11 |

执行单元需要完成的工作归纳起来包括以下几个方面:完成逻辑运算、完成算术运算、完成移位运算、完成比较转移的PC值运算和完成比较后赋值操作。 存储单元首先要实现数据RAM,并完成对数据RAM的读写操作。与指令ROM一样,数据RAM也使用Altera公司提供的宏模块来实现。Minisys拥有4KB的数据RAM,4个字节为一个读写单元,因此,它的RAM和ROM的初始化文件格式相同。

关于Minisys SoC的其他单元的设计将在系统中具体给出。

3. 设计流程图

4. 部分项目仿真图

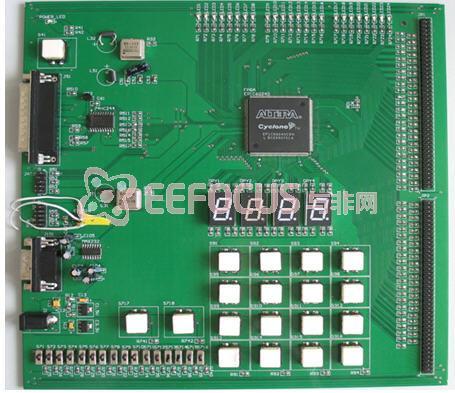

图3 Minisys实验板

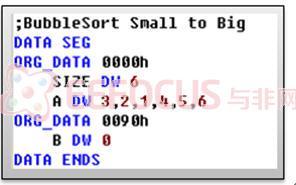

图4 Test1的数据段定义

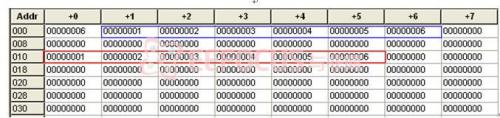

图5 Test1的仿真结果 |