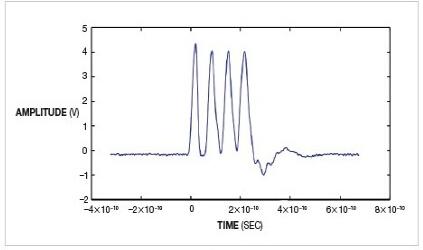

用大多数FPGA都可以实现一个数字UWB(超宽带)脉冲发生器。本设计可以创建一个两倍于FPGA时钟频率的脉冲信号(图1)。以前的设计要采用异步延迟,才能制造出所需频率的脉冲。不过该设计需要一只支持三态上拉的FPGA,如Xilinx公司的Virtex 2。这种方案亦需要手工布局与布线。今天的FPGA都不支持三态上拉。另外,异步延迟会随温度而变化。本例采用了一种有多时钟相位组合的同步延迟方案。这一设计可以实现于所有类别的FPGA上。

本设计中的主要限制因素是DCM(数字时钟管理器)以及触发器的主时钟频率。例如,Xilinx公司Virtex 4的DCM不能超过400 MHz.一片FPGA可以生成频率为时钟频率一半的信号,因为它用两个时钟脉冲使信号从0转换为1,再回到0.因此,不能直接生成大于时钟频率一半的频率。本设计用DCM的多时钟相位以及小于单个时钟周期的同步延迟,可以产生出高于时钟频率一半的脉冲信号,达到时钟频率的两倍。

图1 脉冲的频率可达FPGA时钟频率的两倍

图2即所称的脉冲发生器。它包括三个功能块:一个OOK(on/off键控)调制器、一个同步延迟发生器,还有一个包含一只异或门的边沿结合器。OOK调制器由一只反相器构成,它在每个新脉冲的开始时作为脉冲重复频率信号触发器。当发生一个触发时,OOK电路将一个预初始化的信号转换成为一个时间,该时间等于来自一个脉冲带宽的计数值,然后在下个触发出现前保持为零。OOK块产生的频率是时钟频率的一半。这个OOK输出通过同步延迟发生器,产生出三个延迟版的OOK输出。

图2 设计电路图

这些延迟都小于一个时钟周期。时钟相位依次为触发器FF1、FF2和FF3提供时钟,它们分别延迟90°、180°和270°。这些延迟脉冲再使用组合逻辑,与OOK调幅器的输出相结合,产生出UWB脉冲所需要的频率。边沿结合器完成一次XOR(异或)运算,获得的信号频率取决于希望组合的边沿。将OOK输出边沿与FF1输出相结合,就得到一个等于时钟频率的信号。将所有输出边沿结合起来,就得到一个两倍于时钟频率的信号。DCM对这些延迟做同步,产生一个精确的信号频率。 |