封装技术的进步推动了三维(3D)集成系统的发展。3D集成系统可能对基于标准封装集成技术系统的性能、电源、功能密度和外形尺寸带来显著改善。虽然这些高度集成系统的设计和测试要求仍在不断变化,但很显然先进的测试自动化将对推动3D集成系统的量产产生重要影响。本文将讨论3D集成系统相关的一些主要测试挑战,以及如何通过Synopsys的合成测试解决方案迅速应对这些挑战。

2.5D集成和3D集成

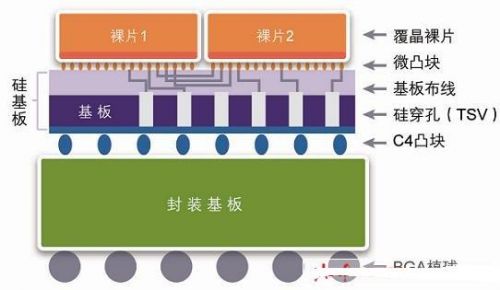

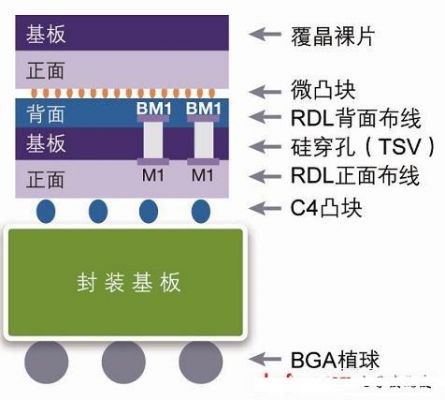

目前有两种基本的3D封装配置。2.5D集成系统在一个普通电气接口(称为硅基板)上挂接多块二维(2D)裸片,并通过穿过基板的导线把这些裸片连接在一起(如图1所示)。系统I/O通过中途延伸穿过基板的垂直硅穿孔(TSV)连接到底层封装基板。由三维堆叠IC(3D-SIC)组成的系统(如图2所示)的外形尺寸比2.5D集成系统更紧凑。在这种配置中,TSV蚀刻在基板中,由2D IC组成的晶片最小厚度不到50微米。多块裸片垂直堆叠并通过TSV进行互连。

图1:2.5D集成(两块裸片通过穿过硅基板的导线进行互连)。

图2:3D-SIC(两块堆叠裸片通过TSV进行互连)。

对堆叠配置进行测试需要2.5D封装测试所需的自动化的超集,因此在以下章节中我们将重点讨论这一话题。

对3D堆叠IC进行测试

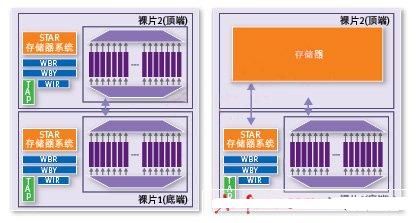

图3显示了由三片裸片堆叠的3D-SIC众多可能测试方法中两种方法的测试场景。一种方法是在所有裸片粘接在一起之后进行堆叠测试,如场景1所示。堆叠测试从底部(第一块)裸片与第二块裸片之间,以及第二块裸片与第三块裸片之间的TSV互连测试开始,然后从底部裸片开始按顺序对每块裸片进行测试。此外,堆叠测试同时还可包括把整个堆叠作为一个集成系统进行测试。

图3:对某个三裸片堆叠进行3D-SIC测试场景举例。在场景1中,只有在所有三块裸片粘接完成之后才进行堆叠测试。在场景2中,每当有一块已知合格裸片粘接到堆叠顶部时都要进行一次堆叠测试。

由于对后续发现存在缺陷的裸片进行“拆除(un-bond)”不太可行,因此在粘接之前对单个IC在粘接过程中的互联可能造成的损失测试可能比仅依赖堆叠测试来识别已造成整个系统缺陷的缺陷裸片更加具有成本效益。在图3的场景2中,每当有一块KGD粘接到IC堆叠顶部时都要进行一次堆叠测试,以便排查对顶部两块裸片以及在粘接过程中的互联可能造成的损失。

尽管把KGD测试纳入3D-SIC测试流程有可能降低总的制造和测试成本,但会带来新的挑战。除底部裸片以外,没有可用于KGD测试的任何探针压焊点,因为所有的I/O都只可通过TSV(顶部有细间距的微凸块,排列在裸片的两侧)接入。业界正在努力建设摆脱这些约束的探针系统,但在新系统可投入生产之前,设计者必须考虑能够利用其现有自动化测试设备(ATE)基础设施的其它方法。一种可行的方法是插入KGD测试专用的“牺牲的(sacrificial)”探针压焊点。虽然存在由于专用探针压焊点而引起的面积损失,但还是可以通过使用DFTMAX压缩中的有限引脚测试功能尽量减少压焊点的数量。有限引脚测试最多可缩短测试应用时间和测试数据量170X,只需要使用一对测试数据引脚。

此外,由于3D-SIC中的故障影响与2D设计中的故障影响完全相同,所以在建立KGD测试模型时仍然可以使用传统的故障模型。但是,由于3D集成系统的外形尺寸比传统设计更小,性能更高,所以高质量的KGD测试可能需要使用TetraMAX ATPG中提供的更高级的测试——比如,针对微小时延缺陷的信号跳变延迟测试和针对桥接故障的桥接测试。

尽管如此,单靠扫描测试并不够。用于连接相邻裸片的TSV数量有数千个,如果没有能够满足3D-SIC细间距要求的探针技术,那么在KGD测试过程中这些TSV的故障是无法观测的。设计者可通过为所有的TSV I/O使用双向I/O包装器单元(wrapper cell)来克服该障碍。TetraMAX可按照双向引脚形式为I/O建立模型,然后生成允许在TSV I/O中应用和捕获数据的TSV“回路”测试,验证其功能。

缺陷驱动型嵌入式存储器自测试是KGD测试的另一个重要组成部分。3D集成系统的设计者可通过Synopsys的DesignWare自测试和修复(STAR)存储器系统为Synopsys和第三方存储器实现最高的缺陷覆盖率。

电源测试注意事项

3D-SIC系统复杂度越高,对动态功耗的控制要求就越高。功耗在裸片粘接到堆叠前后是不同的(因为裸片粘接后TSV为堆叠分配电源)。需要使用功率感知(power-aware)ATPG和基于电源域测试等先进的电源管理技术来限制功耗,从而最大程度地减少3D-SIC测试过程中的误报故障。功率感知ATPG、DFTMAX和TetraMAX协同工作可生成能够把Shift模式和capture模式功耗限制在功能水平(基于设计者指定的开关转换预算)范围以内的模型。

通过基于电源域测试,TetraMAX能够生成符合设计功能电源状态要求的模型,降低动态功率和泄露功率,并尽量减少IR压降问题的发生。此外,它还可通过生成用于测试电源管理电路的模型序列进一步提高缺陷覆盖率。Synopsys的高级电源管理功能已成功部署到2D设计中,以提高缺陷覆盖率和限制ATE上的误报故障。这些高级电源管理功能将在3D-SIC测试中发挥重要作用。

堆叠测试

TetraMAX生成KGD模型后,把KGD模型映射到堆叠级端口是一个简单的过程。对于TSV互连测试,TetraMAX使用动态桥接故障模型生成针对TSV I/O之间时序的全速测试模型。但堆叠测试的主要挑战是设计和实现能够向非底部裸片提供足够测试接口的3D DFT架构,以便进行单独裸片测试,裸片间测试(即TSV互连测试)和可能的多裸片同时测试。Synopsys正积极参与IEEE P1838等新兴3D测试标准的开发。虽然这些标准尚未整合使用,但早期采用者可使用Synopsys的合成测试解决方案来高效地实现基于已确立标准的3D DFT架构。

例如,DFTMAX可为使用IEEE Std 1149.1作为测试接入机制的3D-SIC系统合成、连接和验证JTAG测试接入端口(TAP)和边界扫描寄存器(BSR)逻辑,以便进行KGD或堆叠测试。

此外,DFTMAX还使用IEEE Std 1500标准进行芯核包装和“裸片包装”——当非底部裸片的测试控制接口使用基于IEEE Std 1500标准的包装器时。同样,位于底部裸片并通过JTAG TAP接收指令的DesignWare STAR存储器系统可使用IEEE Std 1500接口为堆叠中所有其它裸片的嵌入式存储器提供必要的测试接入和隔离。

在每块裸片上实现测试接口后,测试接口采用菊花链方式在堆叠内上下互连,实现对逻辑搭载逻辑(logic-on-logic)和逻辑搭载存储器(memory-on-logic)配置的堆叠测试,如图4所示。

图4:Synopsys支持对基于已确立测试接入标准的逻辑搭载逻辑(LoL)和逻辑搭载存储器(MoL)系统进行3D-SIC测试。

能够通过JTAG TAP访问3D-SIC中的嵌入式测试和调试资源的另一个功能是DesignWare SERDES IP(UPx)。Synopsys的高速接口自测试似乎兼容新兴的IEEE Std P1687标准(推荐的仪器使用标准),并且是对3D-SIC产品成功认证和部署起到关键作用的器件接入机制的一个典型类型。除了上述标准以外,Synopsys的测试解决方案使用STIL(IEEE Std 1450.x)和CTL(IEEE Std 1450.6)作为主流接口连接到电子设计和制造行业中的其它系统,并且作为对2.5D和3D封装配置同时进行测试的手段。

摘要

对3D集成系统进行高质量、低成本的测试需要一整套最先进的测试自动化技术,包括有限引脚扫描压缩、功率感知ATPG、基于电源域测试、基于时序违反的全速测试、动态桥接测试、缺陷驱动型嵌入式存储器自测试和修复、高速接口自测试。这些技术目前均已可用,并已完全集成到Synopsys的合成测试解决方案(由DFTMAX、TetraMAX和DesignWare IP组成)中。虽然3D测试接入标准尚未整合使用,但早期采用者已经能够使用Synopsys的测试解决方案(已通过数千个复杂2D系统进行测试证明有效)在实现对3D系统进行测试的同时最大程度地提高设计效率。 |