基于ARM+DSP架构的视频处理系统研究与实现(2)

|

- UID

- 1029342

- 性别

- 男

|

基于ARM+DSP架构的视频处理系统研究与实现(2)

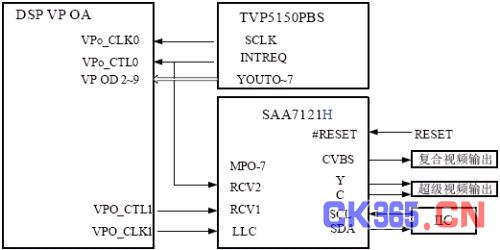

图3 视频输出接口的电路设计

从图3可以看出,VPOA既要作为视频输入口,也要作为视频输出口,但这两种工作模式又不能同时使用。所以,当VPOA作为8位BT.656视频采集口时,仅需视频数据流串行时钟和采集全能控制信号,而这两个信号分别由TVPS 1 SOPBS的SCLK和INTREQ/GPCL/VBLK引脚来控制。此时SAA7121H不起作用。

视频解码接口设计

TVPS 150PBS是一款高性能视频解码器,可将NTSC、PAL视频信号转换成数字色差信号,并支持两路复用视频端子输入,输出格式为ITU-R BT.656,同时它也支持Macrovision复制保护以及高级的VBI功能。

图4 视频输入接口电路图

由图4可见,TVP5150的INTREQ引脚用于控制视频数据流的采集。当INTREQ为1时,允许VP口对输入的视频数据流进行采集;为0则禁止VP口对输入的视频数据流进行采集。VPOA在本系统中还与视频输出SAA7121H相连接,因而VPOA需要工作在Capture与Display两种工作模式。

图5 DSP软件模块结构图

视频处理的软件设计

如前所述,DSP视频处理的软件开发包括应用程序和设备驱动程序两部分。DSP模块软件的结构如图5所示,包括视频采集与回放、ATA硬件存储的设备驱动程序等。

视频采集与回放的设计

DSP的工作状态有三种:一是采集监控状态,即将视频输入和音频采集进程得到的音视频数据经过编码后只保存到内存中,而不写入ATA设备;二是采集保存状态,即将输入的音视频数据经过编码后直接写入到ATA设备中保存;三是回放状态,即从ATA设备中读取以前保存的音视频数据,再解码回放。在第一种工作状态下,DSP可以切换到第二或第三种工作状态;在其他两种工作状态下,DSP只能返回到第一种工作状态。

视频采集模块的软件设计独立于主控模块,其应用程序建立在特定操作系统DSP BIOS之上,每一项具体的操作由主控模块的命令来决定。该模块程序主要包括采集进程、处理进程和回放进程三部分。

其中处理进程是控制整个DSP采集模块的程序,接收主控模块送出的命令,响应具体的命令操作,同时为采集进程和回放进程传送消息,控制其操作。处理进程不仅负责与主控模块的通信,还要将采集得到的视频信息进行H.264的编码,并送给硬盘保存。

采集进程等待处理进程的消息应答,开始采集视频信息后,以帧为单位对视频信息进行处理,将视频信息的原始色彩调整为适合系统输出的值。一帧数据处理完成后,该进程发送消息给处理进程,等待回复后,传递视频数据给处理进程,将控制权交由处理进程决定将视频信息传递给主控模块还是存储在硬盘介质上。

回放进程是在主控模块给出相应的命令后,响应具体的命令,将已采集得到的视频数据回放在监视仪上,以备驾驶员的观察。回放程序的实现,从某种意义上说是采集进程的逆过程。回放程序首先等待处理进程的消息,当得到回放命令后,从硬盘上读取视频数据,还原采集进程处理过的颜色调整,在监视仪上显示该帧视频,如此反复。

图6 视频采集流程图

视频采集模块的软件流程关系如图6所示。

7 结语

ARM+DSP多处理器架构在处理视频处理等方案中可以节约大量空间,简化电路设计,独立调试与开发。本文所研究的基于ARM+DSP架构的系统已经取得了一定的成果。 |

|

|

|

|

|