基于USB3.0协议的PC与FPGA通信系统的设计

|

- UID

- 863084

|

基于USB3.0协议的PC与FPGA通信系统的设计

针对USB2.0在高速数据采集系统中带宽局限问题,设计了一款基于USB3.0总线的高速数据采集接口系统。通过对USB3.0的接口硬件系统、设备固件以及SLAVE FIFO与FPGA接口读写操作的设计,并经过实验测试,USB3.0硬件传输速度可达260 MByte.s-1,连续数据采集传输速率可达100 MByte.s-1且数据保持稳定。

随着USB3.0解决方案的出现,其在保留USB固有优势的基础上大幅提高了数据传输的带宽,适用于高速数据采集领域。本文针对基于USB的高速数据采集系统进行研究,设计了一款基于CYUSB3014芯片的USB3.0高速数据采集接口系统,该系统基于USB3.0协议来实现PC机与FPGA的数据传输。本文介绍了USB3.0固件的设计方法,GPIF II接口特性以及SIAVE FIFO与FPGA的读写操作设计。

1 USB3.0系统结构的设计

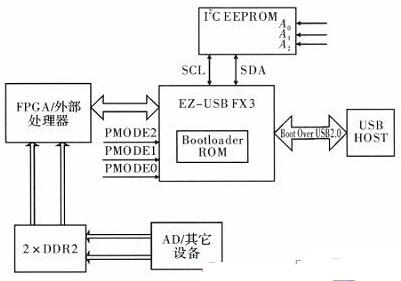

如图1所示,USB3.0系统的主芯片架构为Cypress公司FX3系列CYUSB3014 USB3.0控制芯片、FPGA芯片EP3CA0F484、DDR2芯片MT47H64M16HR.

图1 系统结构框图

CYUSB3014 USB专用控制芯片是新一代USB外设控制器,具有高度集成的灵活特性,可帮助开发人员为任何系统添加USB3.0功能。其拥有工作频率可达200 MHz的32 bit的ARM9内核,使得FX3能够应用在对数据处理要求较高的地方。芯片内部集成了一个512 KByte SRAM,用于存储代码、配置参数,同时用作芯片内部DMA通道的缓冲区。并集成了可编程的100 MHz的GPIF II接口能连接多种类型外部器件,支持最大32个可编程物理端点。

2 FX3固件的设计

固件是用以完成驱动程序无法完成的USB芯片及其外围芯片的初始化及控制工作的代码。FX3固件的主要功能包括:初始化参数的配置、辅助完成设备的重新枚举机制、对中断的处理、数据的接收与发送以及对外围的控制。FX3的固件设计只需调用相应的库函数,而不需要设计者过分关注底层硬件设置,大幅降低了固件的开发难度。EZ—USB FX3的固件设计主要包括对GPIF II接口、DMA通道及回调函数的设计。本文主要对GPIF II接口以及DMA通道加以介绍。

2.1 GPIF II接口

GPIF II接口是FX3与外部设备连接的重要组成部分,利用该接口可以实现与任何外部设备的高速并行数据传输。它具有一个提供多达256个可编程状态的完全可编程的状态机,可实现与任何处理器、ASIC、DSP或FPGA等的设备的无缝连接。GPIF II接口可在100 MHz的工作频率下实现32 bit数据的并行传输,最高有效数据的传输速率可达400 MByte.s-1.该接口可配置为主机模式或从机模式,且数据总线可在8 bit、16 bit及32 bit之间灵活选择。

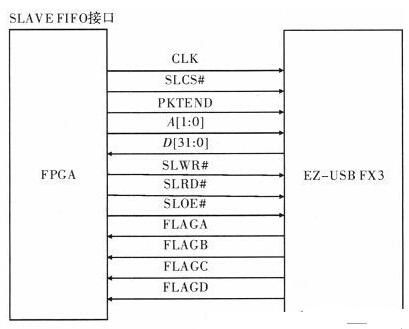

设计将GPIF II接口配置为32位同步SLAVEFIFO模式,外部处理器可像对普通FIFO一样对FX3FIFO进行读写。由PCLK信号作为接口状态机的工作时钟,接口上的地址信号A0:A1表示要访问的线程,FPGA通过检测4个标志信号FLAGA~D来检测缓冲FIFO是空或者满。配置为SLAVE FIFO模式的GPIF II与外部设备的信号连接如图2所示。

图2 SLAVE FIFO接口电路图 |

|

|

|

|

|