电子设计与仿真是电子技术基础学习中的重点内容,是将理论知识转化为实践能力的一个关键环节。文中针对数字电路综合知识的实验要求,设计了篮球赛24 s计时器,并利用Multisim软件进行了仿真。

1设计方案与电路组成

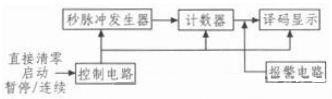

篮球赛24秒计时器是数字电路的简单应用,在设计过程中,采用模块化的设计思路,将该电路划分为:计时电路、控制电路、显示电路及报警电路四部分。

设计方案框图如图1所示。计时电路和控制电路是设计方案中的主要模块,其中计时电路由秒脉冲发生器、计数器构成。计数器完成24 s计时功能,控制电路主要完成计数器的直接清零、启动计数、暂停/连续计数等功能。

图1 24秒计时器设计框图

在设计中,结合实际需求,计数器选取74LS192集成芯片,74LS192是十进制可编程同步加法计数器,它采用8421码十进制编码,并具有直接清零、置数、加减计数功能。利用反馈端和置数端实现进制的转换;秒脉冲发生器由555集成电路或由,TTL与非门组成的多谐振荡器构成。显示电路由74LS48译码器和共阴极七段LED显示器组成。报警电路在试验中可用发光二极管和蜂鸣器代替。

2单元电路设计

2.1信号发生电路

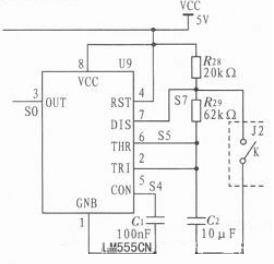

秒脉冲的产生是由555定时器所组成的多谐振荡电路完成。电路图如图2所示。当开关断开时,555定时器产生周期为1秒的脉冲;当开关闭合时,电路无信号输出,故74LS192计数器中无脉冲输入,74LS192计数器维持在保持状态,即实现暂停功能。

图2信号发生电路

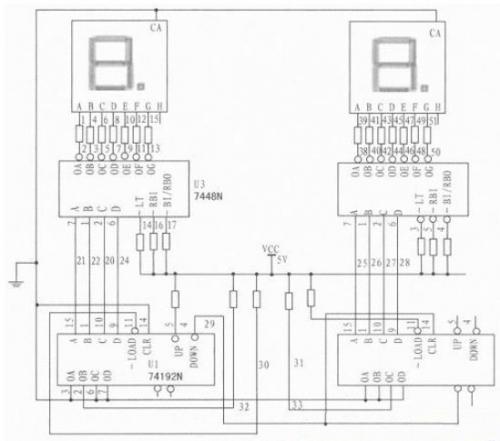

2.2计数电路

用两片74LS192计数器分别作为个位(低位)和十位(高位)的倒计时计数器,本设计只需要从“24”计数到“00”止,因为预置数不为“00”,故选用置数端(LOAD)来进行预置数。时钟脉冲分别通过两个与门输入到74LS192计数器个位(低位)的DOWN端,当停止控制电路传来停止信号时,将中断时钟脉冲,从而实现电路的停止功能。其中,低位的借位输出信号用作高位的时钟脉冲。

两片741S192计数器具体接法:

Vcc、UP接+5V电源,GND接地;

时钟脉冲自与门输出后,连接到低位的DOWN,然后从低位BO‘接到高位的DOWN;

输入端低位C、高位B接电源,其他引脚和CLR接地;LOAD接开关C的活动端,C的另外两引脚分别接G的活动端和地。G的另外两个引脚分别接到电源和地。电路如图3所示。

图3计数电路

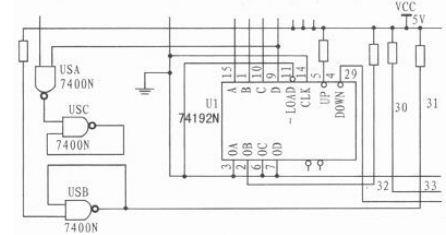

2.3停止控制电路

计数器倒数到“0”时,需要将电路强制转换到“24”并暂停。现选取计数器到零的状态24秒计时到“00”,从各引脚接到二与非门,当计数器从“00”状态转换到“99”时,用与非门把该状态转换成低电平(其余时间为高电平)控制LD,使电路转换到“24”。由于数字“99”显示时间很短,因此在实现从“00”到“24”的转换过程中看不到“99”状态。触发器的输出端输出低电平,使74LS192处于保持状态。这样就实现了转换并停止的控制电路。电路如图4所示。

图4停止控制电路 |