|

- UID

- 1023229

- 来自

- 中国

|

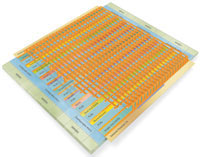

初创公司Cswitch推出一种瞄准网络、无线基站和电信基础设施应用等信息包处理的新颖的可配置逻辑芯片。该器件由异质阵列组成,这一阵列将一排排通用逻辑单元(与传统FPGA中的非常类似)跟一排排可配置SRAM的RAM和CAM(内容地址存储器)模块、ALU(算术逻辑单元)和专门用于信息包处理的模块散布在一起。Cswitch公司总裁兼首席执行官Doug Laird表示,其目的是满足日益增长的如下应用:这类应用必须以线速处理打包数据,而且要使用比传统FPGA速度快得多、功率低得多的器件,还要比ASIC需要的投资少得多,上市时间短得多。事实上,该产品是一种特定应用的FPGA。

其I/O环绕在这种可配置结构周围。可配置SERDES(串行器/解串行器)模块排列在芯片上,它们都能支持PCI Express、XAUI(10GB附件接口)、光纤通道或吉位以太网连接。同样地,可配置MAC(媒体接入控制器)模块也支持这些SERDES模块。其中的一些可编程I/O引脚能够作为可配置的高速DRAM端口,填补芯片的其它两个边。

该结构覆盖的内部芯片设计包括六种可配置模块的相间排列。其中人们最熟悉的可配置逻辑模块采用传统的四输入查找表架构。1GHz八进制ALU可执行有关信息包内容的计算或统计操作。信息包处理模块可以在800MHz条件下对报头和提取的有效负载进行分析。

为了支持这些模块,该芯片提供了1GHz的专用存储器模块,可配置成RAM、主CAM或第三级CAM,以用于缓冲、地址映射、模式搜索,甚至通用表达式处理(只要灵活应用其它模块)。该芯片也有传统的单和双端口RAM行。特定应用架构可提供更小的双端口RAM模块,这些模块可以充当模块间缓冲存储器,以及用于参数和信息包存储的单端口RAM的大型模块。

芯片的互连非常不同于通用FPGA。由于设计人员能够像数据流架构那样加速大多数数据平面信息包的处理,Cswitch不必使用典型FPGA长度和方向变化的互连分段的精细网格,有利于实现简单最近邻正交路由。这类短分段很快且有20位的宽度,而人们能够把它们重新分为5位的若干组。每个分段终止于已配准的完全板上组装的交叉交换点,后者将互连分段连接到逻辑结构中并进行相互连接。因此,一个用于最近邻互连的直通数据通道设计可以成为一条完全配准的流水线。Laird称,这种方法有助于芯片以1GHz的频率接收、编辑、分类和存储信息包。需要较少定序互连的设计必须通过分段和交叉对信号进行菊链式连接,这会导致更长的但高度可预测的互连延迟。

这样一种设计的效用依赖于Cswitch的工具。为此,Cswitch与Magma Design Automation合作开发了一个设计流程,它集成了Blast Create和Blast FPGA工具,以及特定应用库和Cswitch的特定映射和计时文件。实现Cswitch芯片的设计典型地结合了复杂的库功能、各种Cswitch可配置模块的直接实例和Verilog。Magma的产品总监Sanjay Bali说,Magma正从Verilog直接推导Cswitch结构,但仅限于比较明显的情形,诸如映射组合逻辑到逻辑模块上和映射乘法器到ALU上。

目前,Cswitch已在其代工厂特许半导体(Chartered Semiconductor)利用90nm CMOS工艺制作了SERDES模块的测试芯片。 |

|