|

- UID

- 1023229

- 来自

- 中国

|

0引 言

数控电火花(electrical discharge machining,EDM)机床是一种实现工件精密加工的特种加工工具。早期的电火花成型加工机床的脉冲电源电路是用分立元件组成,或者是用单片机来实现。分立元件电路设计复杂,电路调试困难,基于单片机或者是32位的嵌入式CPU的脉冲电源性能有了很大的提高,也具有了很高的智能性,但对于不同的处理器,其移植性不太好,而且如果硬件电路一旦完成就不能进行更改与升级。而采用现场可编程门阵列FPGA在很好的继承单片机或者是嵌入式CPU设计的电源的优点的同时,还拥有一些新的特点。本文提出的方案采用的是Altera公司的cylone II芯片,将Altera提供的NIOS II处理器配置到芯片上,并在NIOS II中加入用户自己用HDL语言编写的可以产生PWM的用户IP模块后就可以产生参数化的脉冲波,即提出了一种新型的智能脉冲电源。

1脉冲电源的原理设计

数控机床的脉冲电源电路主要由脉冲发生器,隔离放大电路,直流电源电路,功率放大电路,开关电路5部分。放电脉冲的产生过程如下,首先是脉冲发生器产生高频参数化的脉冲信号,经过光耦的隔离后,由功率推动电路进行功率放大,从而控制高频开关管的通断。高频开关管的另一端接的是直流电源,该直流电经过开关管的通断而产生高频的放电加工脉冲电源。其核心部分即是脉冲发生器的设计。

2 嵌入式脉冲发生器的设计

只有设计出了高频率的、参数化的脉冲发生器,脉冲加工电源的精度、参数化才可以实现。该电源系统中采用的是性价比较好的Altera公司的Cyclone II序列的FPGA芯片EP2C8Q208C7。其逻辑资源足够实现系统的功能。

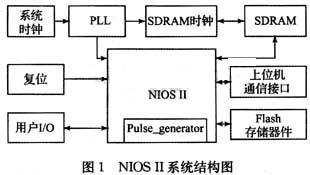

2.1嵌入式系统硬件设计

系统中使用的是一种软核式的Nios II处理器,并选择其类型为Nios/f型。Nios II处理器是Altera的第二代FPGA嵌入式处理器,其性能超过200DMIPS。嵌入式CPU定制的过程是在Quartus II中实现的。Quartus II是Altera提供的FPGA/CPLD开发集成环境,它可以完成系统的设计与仿真。整个设计过程是:图形或HDL编译、分析与综合(analysis&synthesis)、适配器件(filter)、仿真、编程文件汇编(assembler)、下载配置到FPGA。 该系统中除了采用NIOS II和一些常用的外设IP,还有一个用户IP。用户IP用于产生PWM的模块pulse_generator是用VHDL编写状态机来实现的。其中一个模块用状态机实现3种状态:分别空闲、脉宽和脉间。并由时钟输入、状态控制信号以及计数器状态来确定3种状态之间的转换,一般情况是在系统启动后,由空闲状态进入脉宽状态后便会在脉宽、脉间2种状态之间切换,实现连续的PWM。Pulse_generatot的另一个模块就是Pulse_generator与Avalon总线的接口,通过该接口,可以读写Pulse_generator模块中个寄存器的状态,控制PWM脉宽与脉间的大小。在HDL编写好用户模块后,用Quartus进行编译综合正确后,可以进行下一步的寄存器头文件<device_name>_regs.h以及C函数的编写,在该文件的中定义的是用户模块的访问方法,提供了硬件与软件的接口。最后将HDL文件、寄存器文件、驱动程序在SOPC Builder中将其集成成为一个完整的、具有Avalon总线接口的用户IP。将用户IP与Altera的IP结合起来就可以生成硬件的脉冲发生器,它的结构如图1中所示。

构成过程是在SOPC Builder中添加NIOS II、pulse_generator、uart_jatg等模块,然后在SOPCBuilder中generate生成自定制的NIOS II内核,并在工程文件.bdf文件中加入前面生成的NIOSII内核、系统时钟引脚、延时复位、PLL等模块,并将PWM的输出引脚指定到FPGA的I/O口,编译综合后就会生成硬件系统描述的.ptf文件。以上硬件电路全部在FPGA芯片中实现,对用户是不可见的,所以其保密性好,用户外部可见的仅仅是电路的I/O。由于硬件电路是用HDL实现的,因此可以进行系统升级。

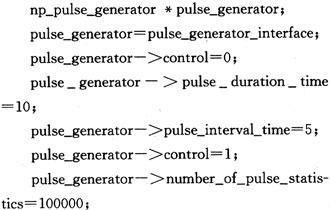

2.2软件编程实现

软件编程采用Altera提供的软件编译环境NIOS II IDE。Nios II IDE基于开放和可扩展的Eclipse平台,不仅可以将通用用户界面和业界最好的开发环境完美结合,还能够与第三方工具无缝地集成在一起。Nios II IDE提供了完整的C/C++软件开发套件,包括编辑器、项目管理器和构建工具、调试器和兼容CFI(common flash interface)的Flash编程器。Altera提供含有支持Micrium的MicroC/OS-II实时操作系统(RTOS)。该系统不用用户修改任何代码即可进行系统移植。使Nios II开发者能很容易地在Nios II IDE中实现多任务软件开发。 软件的开发过程是在IDE中创建一个工程文件,工程所指定的硬件系统即是在Quartus中生成的.ptf文件。新的工程将包括2个库,一个是用户的API库,另一个是系统库,系统的库中包含了用户进行软件编程时需要的各种头文件、驱动程序等。在用户库中可以使用C/++或者是汇编语言编写脉冲参数的实现功能,在写好后就可以对软件工程进行编译、调试得到希望的结果后就可以软件的工程文件.elf下载到开发器件上。如果需要调整脉冲、脉间的参数,则可以在NIOS IDE中对脉宽与脉间的比例以及周期长度进行修改。同时通过对I/O口输出的高低电平,可以控制每一路大功率管的关断与否,从而做到了电流大小的控制,具有非常高的灵活性。这样可以得到新的适合进行粗、中精、精加工的脉冲序列。用户程序中对脉冲控制及参数控制的代码如下:

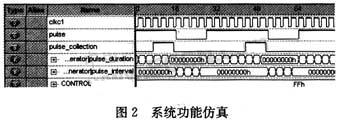

2.2系统仿真

我们可以用Quartus对设计的系统的功能进行仿真,以验证功能是否满足要求。软件文件下载到开发板后对电路进行仿真的结果,如图2所示。从图中可以看到脉宽pulse_duration_time与脉间pulse_interval_time的比例参数,以及控制寄存器的值,同时还可以看到该系统的输入时钟的周期长度,放电脉冲的周期长度等信息。

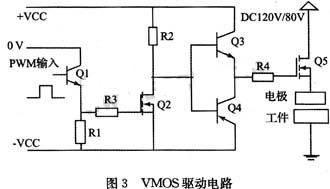

3 外部电路设计

外部电路主要包括直流电源、隔离放大电路、高速开关电路、保护电路。直流电源电路是市电经过变压器、整流桥路电路、电容滤波电路输出的,输出的电压有+80 V和120 V两种,分别用于粗加工和精加工。脉冲发生器的PWM用来控制高频开关管,为了防止脉冲发生器的烧坏,要将FPGA开发板与开关管电路隔离开来,而电源的频率很高,普通光耦的会产生波形畸变,所以采用的是25M的高速光耦PC412S。开关管采用的是VMOS,使用它的好处是开关的频率高,能够承受的电流和电压都比较大,但要使用输入电容较小的VMOS,否则会影响电源关断的速度。开关管的驱动电电路如图3所示。

Q1的基极是从FPGA开发板经过光耦输出的PWM脉冲信号,通过后面的驱动电路来驱动Q5,从而实现放电加工电路中采用正负电源,这样可以提高Q5的关断速度。Q2是小功率的VMOS管,Q3和Q是用来驱动大功率的VMOS,所以功率不能选太小,R3与R4是用来减小系统波形的振荡,其阻值不能太大,可选取100 Ω。

4 结 论

本文在EDM机理与嵌入式技术领域最新研究成果的基础上,针对目前微细EDM加工中电源的研究现状,提出了一种新型的智能型EDM脉冲电源,该电源的脉间精度可以达到0.2μs,是一般的分立软件和集成电路所不能达到的,脉宽,脉间的大小可参数话,这些设置都是在软件中进行,并且采用FPGA设计具有可进行更新,保密性好。这种新型的脉冲电源,由于高电火花脉冲放电频率,从而提高加工精度。又因为HDL语言和FPGA技术的应用越来越广泛,所以这种智能的脉冲电源具有很好的通用性。 |

|