|

- UID

- 852722

|

1 引言

随着半导体工艺技术的发展, 愈来愈复杂的IP核可集成到单颗芯片上, SoC (片上系统)技术正是在集成电路( IC) 向集成系统( IS)转变的大方向下产生的。采用SoC 技术, 可将微处理器、模拟IP核、数字IP核和存储器等集成在单一SoC芯片上, 因而具有很多优势: 采用IP核复用技术可大幅度缩短芯片的研发周期和费用; 采用IP核复用技术能极大改善功耗开销, 降低风冷要求,并可大幅度减少印制板上部件数和管脚数; 由于以前板级连线全部集成到芯片中, 从而带来整机的可靠性的大幅度提高; 可以缩短整机的研发时间和研发费用等。

由于各类IP核质量参差不齐, 到目前为止, IP核的接口标准和质量标准还未完全统一, IP 核质量评估手段还需完善, SoC 芯片集成的IP核越多, 其可靠性降低的风险就越大, 因而非常必要研究多IP核复用SoC的可靠性, 多IP核复用SoC 的可靠性受处理器、外围模块IP核、多IP核间通信的可靠性的影响。

2 SoC芯片可靠性研究

可靠性技术的实现都是以容错为基础, 容错技术主要是依靠资源的冗余和系统重构资源的组织来完成。冗余主要包括硬件冗余、软件冗余、时间冗余、信息冗余等。硬件冗余是在常规的硬件功能设计之外再另加一些备用的附加的硬件, 当常规硬件发生错误时备用硬件起作用, 使系统仍然能够正常工作; 软件冗余是增加一些额外的用于检错纠错的程序, 当运行出错时程序能够自行进行检错纠错; 时间冗余是为某一指令或一段程序开辟额外的时间让其重复执行; 信息冗余是增加信息的多余度, 使其自己具有检错纠错的能力。

从以下三个方面对多IP复用SoC 进行了可靠性研究: 处理器的可靠性、多IP核间通信的可靠性、IP核工作异常状态检测。

2. 1 片上处理器的可靠性

处理器的可靠性直接决定着SoC 芯片的可靠性。从Cache容错、寄存器文件错误保护、触发器的错误保护等方面进行了研究来提高处理器的可靠性, 并分析对整个SoC 芯片可靠性的影响。

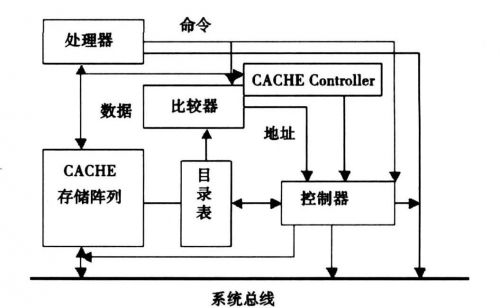

2. 1. 1 Cache容错

在电路中加一个Cache Contro ller 模块, 在该模块中实现对Cache的管理。其中错误检测的方法采用2 位的奇偶校验位, 1位作为奇校验, 1位作为偶校验, 在读Cache的同时进行校验。如果校验出错, 则强迫Cache 不命中, 并从外部存储去获取数据。CACH E的控制结构如图1所示。

| | 图1 |

|

|