RMII模式以太网PHY芯片DP83848C的应用(2)

|

- UID

- 1029342

- 性别

- 男

|

RMII模式以太网PHY芯片DP83848C的应用(2)

2.3 TXD[1:0]——发送数据 TXD[1:O]的变换相对于REF_CLK是同步的。TX_EN有效后,PHY以TXD[1:0]作为发送端。

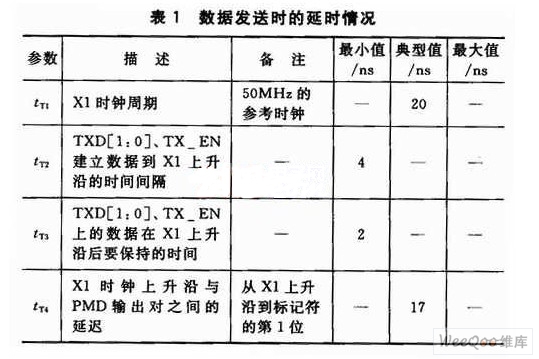

在10 Mbps模式下,由于REF_CLK的频率是在10Mbps模式中数据速率的10倍。因此TXD[1:0]上的值必须在10个脉冲期间保持稳定,确保DP83848C能够每隔10个周期进行采样。发送时序如图5所示,发送延时情况如表l所列。其中,PMD为物理介质关联层(physical media depen-dent)接口。

2.4 RXD[1:0]——接收数据

RXD[1:0]转换是与REF_CLK同步的。在CRS_DV有效后的每个时钟周期里,RXD[1:O]接收DP83848C的两位恢复数据。在某些情况下(如数据恢复前或发生错误),则接收到的是RXD[1:O]的预确定值而不是恢复数据。CRS_DV解除确认后,RXD[1:O]为“00”,表示进入空闲状态。CRS_DV确认后,在产生正确的接收解码之前,DP83848C将保证RXD[1:0]=“00”。

DP83848C提供的恢复数据总是半字节或成对双位信号的形式,这对于由前导符开始的所有数据值都成立。因为CRS_DV是异步确认的,不能假设先于前导符的“00”数据会是双位信号形式。

100 Mbps模式下,在CRS_DV确认之后的正常接收过程中,RXD[1:O]将会保持“00”,直到接收器检测到正确的起始串分界符(Start St-ream Delimiter,SSD)。一旦检测到SSD,DP83848C将会驱动前导符(“01”),后面紧跟着起始帧分界符(Start of Frame. Delimiter,SFD)(“01”“01”“01”“11”)。MAC应该开始SFD之后的数据。如果检测到接收错误,在载波活动结束前,RXD[1:0]将会替换为接收字符串“01”。而由于帧中剩余数据被替换,MAC的奇偶校验将会拒绝错误的信息包。如果检测到错误的载波(坏的SSD),RXD[1:O]将会替换为“10”,直到接收事件结束。这种情况下,RXD[1:O]将会从“00”变为“10”,而无需标明前导符(“01”)。

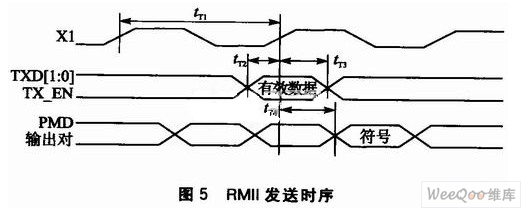

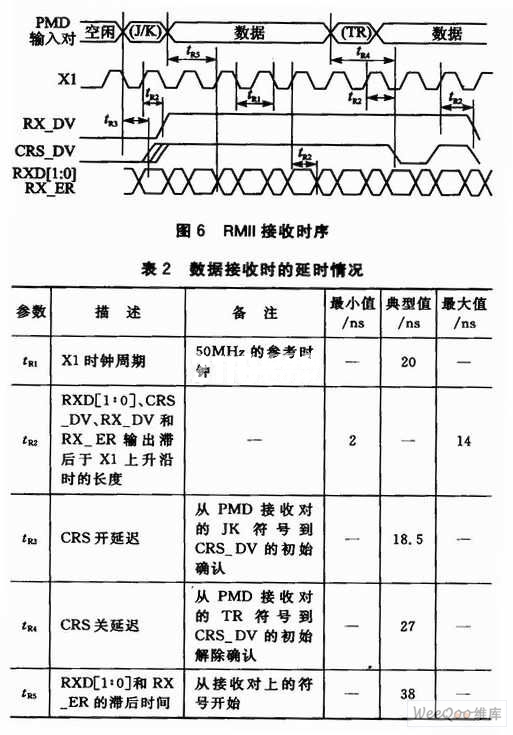

10 Mbps模式下,CRS_DV确认后,RXD[1:O]将会一直保持“00”,直到DP83848C有恢复脉冲并能对接收数据进行解码为止。当存在有效接收数据时,RXD[1:O]以“01”为前导符接收恢复的数据值。因为REF_CLK频率是10 Mbps模式下数据速率的10倍,MAC对RXD[1:0]上的值每隔10个周期采样一次。接收时序如图6所示,接收延时情况如表2所列。

2.5 RX_DV——接收数据有效

尽管RMII并不要求,DP83848C还是提供了一个RX_DV信号。RX-DV是没有结合CRS的接收数据有效信号(Receive Data Valid)。第一个正确的恢复数据(前导符)或伪载波检测到来时,RX_DV被确认,在恢复数据的末两位传送之后解除确认。通过使用该信号,全双工MAC不必再从CRS _DV信号中恢复RX_DV信号。

2.6 CRS_DV——载波侦听/接收数据有效

当接收介质处于非空闲状态时,由PHY来确认CRS_DV。在载波检测中,CRS_DV依据与工作模式相关的标准异步确认。10BASE_T模式下,静噪通过时发生该事件。在100BASE-TX模式,当10位中检测到2个非相邻的零值时,发生该事件。

在RMII规范(1.2版)中提到,载波丢失将导致与REF_CLK周期同步的CRS_DV解除确认,这在RXD[1:O]半字节的首两位出现(即CRS_DV仅在半字节边界解除确认)。在CRS_DV首次解除确认后,如果DP83848C还有数据位要加在RXD[1:O]上,则在REF_CLK周期中,DP83848C应在每半个字节的第2个双位上确认CRS_DV,并在一个半字节的第1个双位解除确认。这样,从半字节边界开始,到CRS(载波侦听/接收信号)在RX_DV前结束时,CRS_DV以25 MHz(100 Mbps模式)或2.5MHz(10 Mbps模式)的频率翻转(假设当载波事件结束时DP83848C还有待传送的数据位)。

通过编程DP83848C能够与RMII规范(1.0版)很好地兼容。在该模式下,CRS_DV将会异步地与CRS进行确认,但是要等传送完最后的数据时才会解除确认,CRS_DV在数据包的末端不会被翻转。该模式虽然不能对来自CRS_DV的CRS信号进行精确的恢复,但是却可以使MAC层的设计更简单。

在出错的载波活动时间中,CRS_DV保持确认。一旦确认CRS_DV,则可以认为在RXD[1:O]上的数据是有效的。然而,由于CRS_DV的确认相对于REF_CLK是异步的,因而在正确解码接收信号之前,RXD[1:0]上的数据应为“00”。

2.7 RX_ER——接收错误

遵照IEEE802.3标准的规定,DP83848C提供一个RX_ER输出端。RX_ER可以维持一个或更多的REFCLK周期,来标识一个在当前PHY到帧的传输过程中曾出现的错误(MAC子层不一定能检测到,但PHY可以检测到的编码错误或其他错误)。RX_ER的变化相对于REF_CLK是同步的。

由于DP83848C是通过以固定数据代替原来数据的方式干扰到RXD[1:O],所以MAC不需要RX_ER,而只需CRC校验(即奇偶校验)就可以检测到错误。

2.8 冲突检测

RMII不向MAC提供冲突标志。对于半双工操作,MAC必须从CRS_DV和TX_EN信号中产生它自己的冲突检测。为了实现这一点MAC必须从CRS-DV信号中恢复CRS信号,并和TX_EN进行逻辑与。注意,不能直接使用CRS_DV,因为CRS_DV可能在帧的末端触发以标志CRS解除确认。

3 RMII模式配置

DP83848C的RMII模式配置包括硬件和软件两个方面。

3.1 硬件配置

如图2所示,DP83848C的X1(34)脚上提供50 MHzCMOS电平的振荡信号。在上电和复位时,强制DP83848C进入RMII模式。方法是通过在RX_DV/MII_MODE(39脚)接入一个上拉电阻。

3.2 软件配置

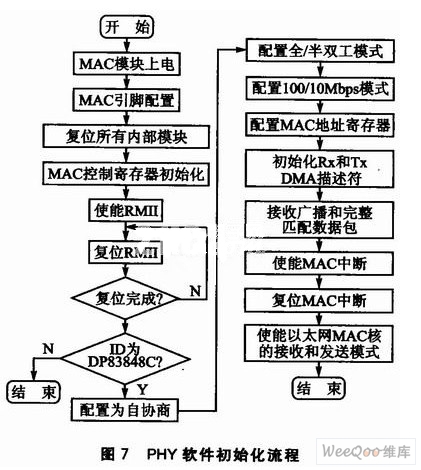

PHY的软件初始化流程如图7所示。

结语

DP83848C配合RMII标准接口提供了一种连接方案,可以减少MAC至PHY接口所需要的引脚数目。该方案使得设计工程师在保持IEEE802.3规范中所有特性的同时,降低系统设计成本。正因为如此,DP83848C能够更好地适应工业控制和工厂自动化,以及通用嵌入式系统等应用场合。 |

|

|

|

|

|