����EEPROM�Դ�����FPGAоƬ����ʵ�ִ��м���֮һ

|

- UID

- 1023229

- ����

- �й�

|

����EEPROM�Դ�����FPGAоƬ����ʵ�ִ��м���֮һ

ժ Ҫ�� ͨ���Աȶ���FPGA���ݼ��ط�ʽ���ӿɿ��ԡ������Լ�PCB��Ƶȼ�������˵���˴��м��ص���Խ�ԣ�������Ŀǰ���м��������ٵ����⡣Ϊ������м��������ٵ����⣬����˲���EEPROM��9500ϵ��CPLD����ʵ�ִ��м��صĹ��룬��ͨ��ʵ����ƣ��ɹ���ʵ���˸ù��롣

�ؼ��ʣ� FPGA CPLD EEPROM ������ת��

�Դ��ģ�ֳ��ɱ�������������������Ⱥ����������������һ���ǻ���SRAM��ϵ�ṹ��FPGAϵ�У���XILINX��˾��4000ϵ�к����µ�Virtexϵ�У���һ���ǻ���faxtFLASH������CPLD��������XILINX��˾��9500ϵ�к�Lattice��˾��ispLSxxϵ��оƬ��FPGA���������������Դ�ḻ��Ƭ��ROM��RAM��������ص�1������������Ҫ��ÿ���ϵ�ʱ�������ݼ��ء�Ŀǰʵ�ּ��صķ������������֣��ٲ���PROM���м��أ��ڲ���ר��SROM���м��أ��۲��õ�Ƭ������ʵ�ּ��ء���һ�ַ�ʽ��Ҫռ�ý϶��FPGA�ܽ���Դ����Ȼ��Щ�ܽ��ڼ�����ɺ������һ��I/O�ڣ����ڼ���ʱ��������Щ�ܽ��������κ������ź�Դ���������ݴ洢��PROM��FPGA֮��Ĵ����̶�������8λ�������Լ���������PROM�ĵ�ַ�ߵȣ�ʹ��PCB��Ʋ��㡣���ǵ�һ�ַ�ʽ��һ�������ķ��棬��PROM�������ϴ������á��۸�͡�����֧��(�����)�Ϻá��ڶ��ַ�ʽ����պ����һ�ַ�ʽ�෴����ռ����Դ�١�PCB���巽�㣬��������С���۸�ϸߡ������Բ�����ַ�ʽ���õ�Ƭ�����ƣ���PROM�ж�ȡ�������ݣ�Ȼ���ٴ����ͳ��������漰����Ƭ����̣����ڿ�������˵��Ϊ���㣻���⣬�����Ƭ��������ʵ�ָ�����Ϊ�˷�Ӳ����Դ��CPLD��һ������ŵ��Dz��ü����ר�ÿ������ߣ�ͨ��JTAG��ֱ��һ����ʵ�ֱ�����ݼ��أ������ñ��������ǽ����ٴα��(��GAL��������)�����������Ƚ��ʺ���ʵ�����ڽ����ֳ����ԣ��������������ݵļ��ر���ͨ�����������˶��ڴ���Ұ����ҵ����˵��������㡣

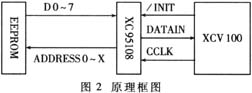

ͨ�������Ƚϣ������ʵ�ʹ��������������Ϊ���ô������ݼ��رȽϷ��㡢�ɿ�(���ֿɿ��Ե�����FPGA��SROM֮����ٵĽӿ���)��������FPGA��ģ�IJ�����������CONFIG������Խ��Խ��ֹ������д��ʱ��CONFIG����������ѵ�6MBIT����ȻXILINX��˾����ص�XC17Xϵ��SROM�ṩʹ�ã�����Ϊһ����оƬ��2�������ɱ��ϸߡ������̹������ڳ����۸�ϸߣ����FPGA��Ӧ�ü��ռ������ܴ���ϰ���������ʹ�ù�AT��T��˾��ATT17ϵ�е�ɲ���SROM�����Ǹ���SROMоƬ����XILINXϵ��FPGAоƬʵ�ֽӿڵ�����࣬������С����������ԭ����۸�������ͬ���洢������EEPROM���塢�������������ߣ�������Դ���ѡ���ô�ܲ��ܽ�ϲ��м����봮�м��ص��ŵ㣬�Ӷ����������FPGA���ݼ��ص������أ���������ϸ�����˴��м��ػ��ƺ���Ϊ����EEPROM��Ϊ���ݴ洢���������ɿصIJ�����ת����Ӧ�ÿ���ʵ�����ݼ��ء�������XILINX��˾Virtexϵ��XCV100оƬΪ��������ATMEL��˾1��λ��AT29C010A�������ݴ洢������XILINX��˾9500ϵ��XC95108оƬ��Ϊ���ؿ�������������ơ�

1 ԭ�����

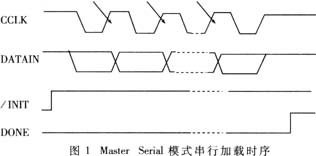

ԭ����Master Serialģʽ���м���ʱ����ͼ1��ʾ

�ڸü���ģʽ�У��Ƚ���Ҫ�ļ����ź�Ϊ/INIT��CCLK��DATAIN��DONE��/INIT��ʾFPGAоƬ�ϵ�ʱ���ߵ�/PROGRAM�ź�Ϊ��ʱFPGA�ڲ����ݳ�ʼ�����̣�����Ϊ�����źŸ����ݼ��ؿ���������Ϊ��λ֮�á���/INIT�ź�ԾΪ�ߵ�ƽʱ��CCLK��ʼ��������������DATAIN��CCLK�������ش��룬��ͨ�ô���ͨѶ�����ƣ�����������Ҳ�п�ʼλ�����λ����������֡�ķ�ʽ���ա�һ����������FPGA����ֹͣ�������ݣ�����/INIT�ź���Ϊ�͵�ƽ����˸��ź��ֳ�Ϊ����ָʾ�źš�������ȫ�����ܲ���֤�����FPGA��DONE�ź���Ϊ"1"��3�� �ڷ�����FPGA�������������Ժ��Եó�����һ�����ۣ���֤CCLK��DATAIN֮����ϸ�ͬ���������ԣ��Ϳ���ʵ�ּ��ء����ڴ˽��ۣ������ɼ������ݸ�ʽʱ��������ƬSROM���и�ʽ������XILINX��˾��FPGAϵ�У��ø�ʽΪ��MCS�ļ���ʽ��Ȼ����ALL07�������INTEL HEX���ݸ�ʽ����д��EEPROM�С����µĹ�������CCLK��/INIT��DATAIN�Ŀ�������ɲ�����ת�����ÿ��ƹ��̲���һƬCPLD֮95ϵ��XC95108оƬ���е�������������ϲ���һƬXC9536������ɣ�֮���Բ���XC95108����Ϊ������Ҫ�������������ԭ����ͼ��ͼ2��ʾ��

|

|

��¼ѧϰ�еĵ��εΣ���ÿһ����ĸ��������壡 |

|

|

|

|

|