|

- UID

- 1023229

- 来自

- 中国

|

视频监控系统在火车站、机场、银行、娱乐场、商场甚至家庭的安保方面都是一种关键设备。随着安全风险的日益增大,在各种应用场合对已发事件进行视频监控和记录的需求都在逐步上升,这就要求视频监控系统的新结构必须具备可扩展性,以便为日益多样化的视频监控需求提供高性价比的解决方案。

在视频监控系统结构所面临的众多挑战中,上市时间压力、CODEC新标准的出台和需求范围的不断扩大(包括高级目标检测、运动检测、目标跟踪和目标跟踪功能) 还只是其中的一小部分。要应对这些挑战,视频监控系统的实现就必须能根据不同性能要求而进行相应调整。

Xilinx的 FPGA产品是各种视频监控系统理想的解决方案,不论它是低端系统还是高端系统,是独立系统还是PC扩展卡系统。

视频监控与DVR系统

高级数字视频压缩技术在视频监控系统的数字录像机(DVR)中正得到快速普及。随着大多数DVR制造商从MPEG4转为采用H.264 高清(HD) CODEC,对提高分辨率和压缩率的要求也变得更急切。专用标准产品(ASSP) 比较适合量大的应用,但缺乏灵活性,而且开发时间过长,成本也高。大多数高级数字媒体处理器连实现H.264 HD解码都比较困难,何况H.264 HD编码比解码还复杂得多。因此,要满足H.264 HD的性能要求,最佳方案就是采用一块FPGA加一块外部DSP或数字媒体处理器。

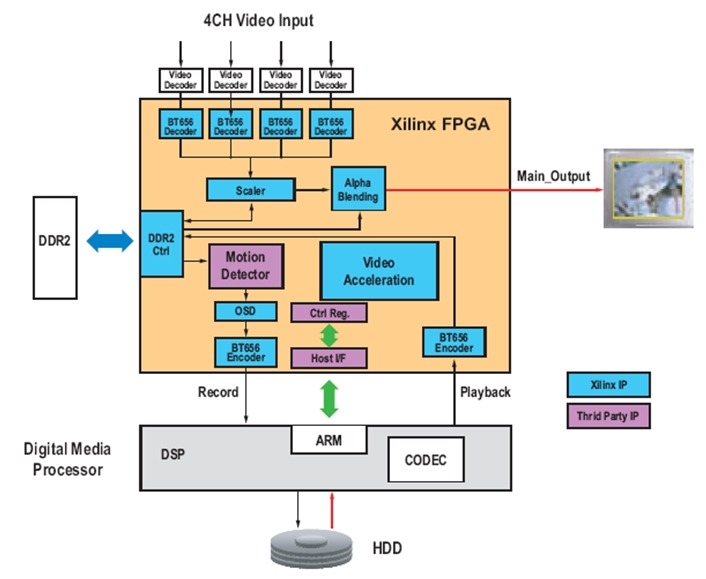

采用低成本的Xilinx FPGA产品还能进一步提供运动检测、视频量化、色域转换(color-space conversion)、硬盘接口、DDR2存储器接口等功能,以及将两个27MHz的 ITU-R BT656数据流通过时分复用合为一路54MHz的数据流,同时为DSP处理器提供视频加速。将两个ITU-R BT656数据流复用为一个之后,系统只需单通道的视频端口就能独立传送整个双通道的视频数据。这种实现方式在连接只有一个ITU-R BT656视频输入端口的数字媒体处理器时非常实用。图1所示就是上述推荐系统的结构框图。

图1:利用FPGA和数字媒体处理器搭建的视频监控系统。

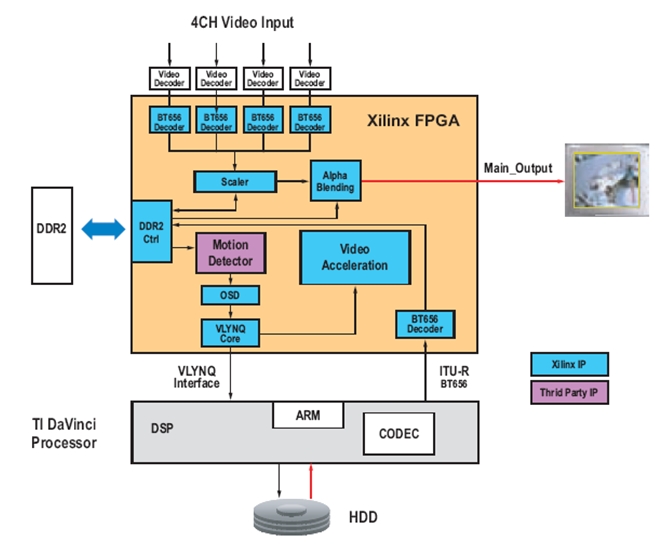

对采用只有单个ITU-R BT656视频输入端口的TI达芬奇处理器的DVR设计而言,更高效 的实现方案是在数据流送入达芬奇处理器之前,将两个以上的ITU-R BT656数据流时分复用为单个VLYNQ数据流。这种方案减少了用于视频数据流传输的I/O管脚,因而缩小了器件的封装,降低了系统成本。图2所示为该设计的框图。

图2:利用FPGA和达芬奇处理器搭建的视频监控系统。 |

|