基于Cadence_Allegro的高速PCB设计信号完整性分析与仿真(3)

|

- UID

- 1029342

- 性别

- 男

|

基于Cadence_Allegro的高速PCB设计信号完整性分析与仿真(3)

2 基于Cadence_Allegro的仿真结果及分析

2.1 高速14位ADC/DAC应用系统简介

如图2所示,该应用系统可做ADC/DAC芯片验证,基于Cyclone2系列的FPGA,可实现DDC,DDS功能。实际应用中待测ADC选用Linear公司14位105 MS/s的芯片LTC2284,DAC芯片采用AD公司14位、210 MSPS的芯片AD9783,系统PCB设计如图2所示。

2.2 对AD时钟信号的反射仿真与分析

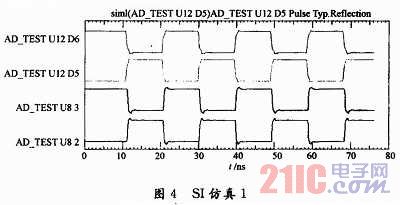

仿真主要基于IBIS模型,它是用于描述I/O缓冲信息特性的模型,它可以将一个输出输入端口的行为描述分解为一系列的简单的功能模块,由这些简单的功能模块就可以建立起完整的IBIS模型。本应用系统时钟是由FPGA软件倍频后经由时钟缓冲器件分配到ADC,DAC网络的。提取的由FPGA锁相环到时钟缓冲芯片的拓扑结构如图3所示。

对其SI仿真如图4所示。

由图4可知,由于合理的布局布线,高频差分时钟信号经过传输线时信号发生的变化极小,保持了较好的质量。 |

|

|

|

|

|