|

- UID

- 1029342

- 性别

- 男

|

PCI Express(PCIe)是一种高性能互连协议,可应用于网络适配、图形加速、服务器、大数据传输、嵌入式系统等领域。PCIe协议在软件层上可兼容于PCI和PCI—X,但同时也有明显的不同。在两个设备间,其是一种基于数据包、串行、点对点的互连,因此所连接设备独享通道带宽。根据使用的版本号和通道数,其性能具有可扩展性。对于PCIe 2.0,每条通道在每个方向上的数据传输速率是5.0 Gbit·s-1。从PCIe×1~PCIe×16,能满足一定时间内出现的低速设备和高速设备的需求。

Altera提供了兼容于PCIe 1.0和PCIe 2.0的解决方案,无论是作为根节点还是端点,都可以通过嵌入在FPGA内部的可配置硬核IP模块实现,而不占用可编程资源,这既节省了资源也提高了应用的可靠性。Altera的IP编译器可以提供×1,×2,×4,×8的通道接口。本文主要介绍采用Cyclone IV GX系列的FPGA来实现×4的PCIe接口所涉及的硬件电气规范、协议规范等。

1 PCIe总线体系和Cyclone IV GX

1.1 PCIe总线体系概述

PCI Express是一种基于数据包、串行、点到点的高性能互连总线协议。其定义了一种分层的体系结构,包括软件层、处理层、数据链路层和物理层。其中软件层是保持与PCI总线兼容的关键,PCIe采用与PCI和PCI—X相同的使用模型和读写通信模型。支持各种常见事物,如存储器读写事物,IO读写事物和配置读写事物。而且由于地址空间模型没有变化,所以现有的操作系统和驱动软件无需进行修改即可在PCIe系统上运行。此外PCIe还支持一种称为消息事物的新事物类型。这是由于PCIe协议在取消了许多边带信号的情况下,需要有替代的方法来通知主机系统对设备中断,电源管理,热插拔支持等进行服务。

1.2 Altera Cyclone IV GX系列FPGA

Cyclone IV GX FPGA采用Altera成熟的GX收发器技术,具有出众的抖动性能和优异的信号完整性。利用灵活的收发器时钟体系结构,可充分利用收发器所有可用资源,实现多种协议。Cyclone IV GX FPGA为根端口和端点配置的PCI Express×1、×2和×4提供唯一的硬核知识产权(IP)模块。因此不用再接入其他专用的PCIe协议芯片,即可实现端到端的高速数据传输。

Cyclone IV系列的FPGA还支持一系列外部存储器,包括DDR2 SDRAM,DDR SDRAM,QDR SDRAM。Altera可提供速度最快、效率最高、最低延迟的存储器控制器,使得FPGA可以接入现有的更高速的存储器件。专用的DQS和DQ引脚在芯片级的布线上进行优化以减少抖动和增大余量上,且固定在芯片四周的特定位置。高速外部存储器在众多应用中是重要的系统组成部分,如视频图像处理,数据通信与存储,以及DMA等。

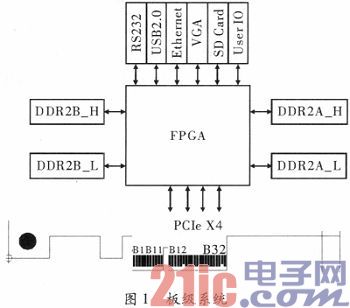

2 板级系统和部分走线阻抗

2.1 板级系统

充分利用FPGA左右两侧的存储器接口,分别挂两片Micron的DDR2 SDRAM颗粒,作为DMA缓存。FPGA的下侧是高速收发器接口,共有4组GXB[3:0],分别经差分链路接入PCIe ×4金手指。其中GXB[3:2]是复用接口,通过改变T节点的耦合电容,可接入两路高速ADC。FPGA上侧接口包括USB PHY、千兆以太网PHY、串口、SD卡以及VGA接口等。FPGA有3个时钟输入,分别是:(1)来自PCIe接口的参考时钟PCIE_REFCLK。(2)来自专用时钟模块的GXB_REFCLK。(3)来自25 MHz有源晶振的SYM_CLK。 |

|