|

- UID

- 1023229

- 来自

- 中国

|

3、PLD同单片机AVR读写接口VHDL实现

PLD的设计流程[6,7]一般应包括以下几部分:

① 设计输入。可以采用原理图输入、DHL语言描述、EDIF网表读入或波形输入等方式。

② 功能仿真。此时为零延时模式,主要检验输入是否有误。

③ 编译。主要完成器件的选取及适配,逻辑的综合及器件的装入,延时信息的提取。

④ 后仿真。将编译产生的延时信息加入到设计中,进行布局布线后的仿真,是与实际器件工作时的情况基本相同的仿真。

⑤ 编程验证。有后仿真确认的配置文件下载到PLD相关配置器件中,加入实际激励,进行测试,以检查是否完成预定功能。

以上各步骤若出现错误现象,则需要重新回到设计阶段,修正错误输入或调整电路,在重复上述过程直到其完全满足电子系统需要。

本系统中,使用Altera公司提供的集成开发软件Quartus II 6.0 进行设计,在进行模块实现时请参考ATmega64L的数据手册中关于ATmega64L对外部存储器的读写时序。

本设计实现的VHDL部分源码如下:

地址锁存:

process(ale)

begin

if ale event and ale=0 then

add<=mcu_data;

end if;

end process;

写数据进程:

process(wr)

begin

if wr=’0’then

if((cs=0) and (add=00000000))then

conreg1<=mcu_data; --把数据写入地址0的寄存器REGl

end if;

if ((cs=0) and (add=00000001)) then

conreg2<=mcu_data; --把数据写入地址1的寄存器REGl

end if;

end if;

end process;

读数据进程:

process(rd)

begin

if rd=0 then

if((cs=0) and (add=00000000)) then

bus_data<=reg01; --从地址为0的REG01寄存器读数据

elsif ((cs=0) and (add=00000001)) then

bus_data<=reg02; --从地址为1的REG02寄存器读数据

else

bus_data<=ZZZZZZZZ;

end if;

else

bus_data<=ZZZZZZZZ;

end if;

end process;

4、仿真验证结果

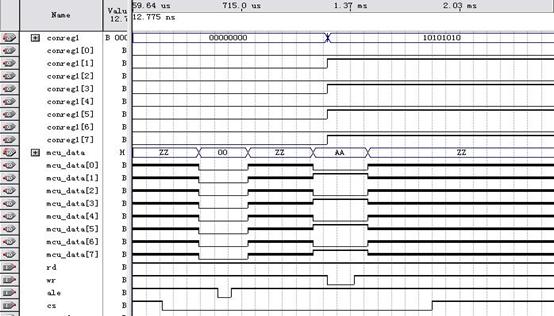

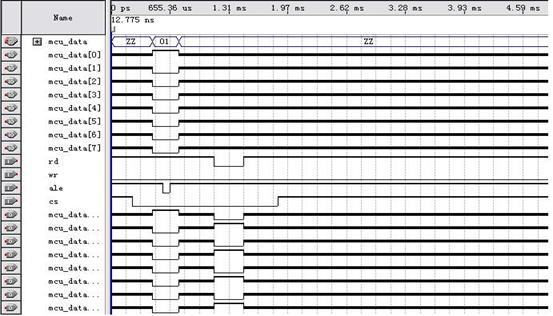

使用Quartus II 6.0 自带的仿真软件仿真结果如图2和图3所示。图中ale、cs、rd、we、mcu_data 是激励信号,表示ATmega64L 相应接口信号,conreg1和 conreg2 为EPM570 输出信号,其目的是为了观察仿真结果是否正确,而实际应用中应根据项目需求而进行添加或是减少相应的I/O口。

图2是ATmega64L向 EPM570 写数据过程。首先,在片选信号cs为低期间,在ale信号的下降沿,锁存mcu_data上的数据到add内部地址锁存寄存器。然后,在we信号低电平时,把mcu_data (0XAA)的数据直接写到conreg1(B10101010),通过外接指示灯可以直接观察结果是否正确,当然,在实际应用中可以把数据锁存到内部寄存器中。

图2写数据0X“AA”到0地址处

图3是读数据过程。在片选信号为低期间,首先,在ale信号的下降沿,锁存mcu_data(0X01)数据到add内部地址锁存寄存器。然后,在rd信号的低电平期间,把内部寄存器地址为0X01的数据reg02(0xAA)读到mcu_data数据线上传回单片机ATmega64L。

图3 读地址为0X“01”上的数据0x“AA”并传回数据总线

从读写数据图中可以看出,ATmega64L对EPM570内部数据读写过程完全满足ATmega64L数据手册上的时序需要。关于ATmega64L的读写时序可以参考ATmega64L数据手册。

5、结语

本文实现PLD与AVR ATmega64L通信接口设计是笔者设计的一种纺织机械控制设备的一部分,经实际验证完全正确,并已投入生产。简单地修改该读写通信模块,可应用于多个CPLD或FPGA与单片机通信接口的项目中,本模块还可以根据需要扩展为16位、32位地址线的读写接口。

本文创新点:充分利用可编程逻辑器件丰富的I/O口和内部可编程逻辑资源,通过总线读写的方式通讯,使PLD和MCU的通信速度大大提高,同时也提高了嵌入式系统或是工业控制中的其他相关性能,极大提高产品的竞争力。

参考文献

[1]乔庐峰(译). VHDL数字电路设计教程. 北京: 电子工业出版社, 2005.

[2]白云飞. 现场总线的技术特点和发展趋势. 机械管理开发-2007年1期.

[3]李家星. 基于嵌入式系统和FPGA的通用总线控制器的设计与实现[J].微计算机信息,2007,1-2

[4]金春林,邱慧芳等. AVR系列单片机C语言编程与应用实例. 北京:清华大学出版社,2003.

[5]潘松. VHDL实用教程. 成都: 电子科技大学出版社, 2000.

[6]杨刚,龙海燕. 现代电子技术—VHDL与数字系统设计[M]. 北京: 电子工业出版社, 2004.

[7]蒋璇,臧春华. 数字系统设计与PLD应用. 北京: 电子工业出版社, 2005.

[8]杨宗凯. 数字专用集成电路的设计与验证[M]. 北京: 电子工业出版社, 2004.

作者简介:秦长江(1981- ),男,四川人,东华大学硕士。主要研究方向是:嵌入式系统,智能控制;余子全(1982- ),安徽人,东华大学硕士。主要研究方向是:嵌入式系统,普适计算;李玉泉(1983- ),男,山东人,东华大学硕士。主要研究方向是:嵌入式系统,普适计算;曹奇英(1960- ),男,教授、博士生导师。主要研究方向是:嵌入式系统,普适计算,网络安全,数据挖掘。 |

|