|

- UID

- 1023229

- 来自

- 中国

|

本系统的工作频率选取100MHz,则FIR滤波器的采样频率fsample默认为100MHz。信源的码速率为2Mbps,经编码、串并转化产生I、Q两路信号的速率为1Mbps,升余弦的滚降系数选取α=0.25,则fcut =[(1+α)/2]* 1=0.625MHz,此时fsample/fcut=160,比值过大,要达到滤波效果需要大幅度提高滤波器的阶数,所占的硬件资源也大幅增加。上述情况是由于滤波器模块的工作时钟默认为系统时钟的缘故。通过优化系统,在Quartus II的环境下可改变滤波器的工作时钟。通过使用计数器将系统时钟十分频,得到一个10MHz时钟,用该时钟来控制滤波器的工作,可以降低对滤波器阶数的要求,减少FIR滤波器所占的硬件资源。另外,输入总线宽度设为2,输出总线宽度设为12。

C. 数控振荡器(NCO):NCO IP core在发送端产生10MHz的正、余弦载波对成形滤波后的信号进行上变频的调制发送;在接收端同样产生一个10MHz的载波对接收数据进行下变频。

NCO产生正余弦载波的[3]函数表达式:S(nT)=Asin[2π(f0+fFM)nT+ΦPM+ΦDITH,其中A=2N-1, f0=Φincfclk/2M。N为幅度的精度,M为累加精度。

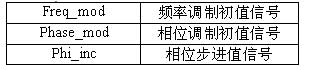

NCO的主要控制信号如下:

配置以上三个值使NCO输出指定频率和相位载波。当需要对输出频率进行微调时便可以通过对频率调制初值信号和相位调制初值信号进行设定。已知系统频率fclk=100MHz,设定NCO的累加精度为24bits,通过计算得出相位控制字:Φinc=2M * fo /fclk=224*107/108 = 1677722,便可以得到10MHZ的载波。

3.2 其它模块的设计

A. 信源模块:信源核心部分是一个由DSP_Builder提供的M序列发生器模块,该模块的使能信号由系统时钟50分频产生。数据经串并转化模块转化成8bits宽度的数据后等待输入到编码器。同时,信源模块还需要产生串/并、并/串模块的控制信号,以及各个IP core的控制信号。(产生的信源是204个符号一组,其中末尾以16个零结束)

B. 差分编解码模块:差分编码是为了抑制因为相位模糊而出现的数据反相及错路现象,本系统采用了两路联合差分编码方式,将I、Q两路信号进行模四加运算。

C. 相位检测模块:该模块通过采用COSTAS环实现对本地时钟和调制载波时钟的相位误差检测。相位误差提取公式为:e(k)=I(k)sign(Q(k))-Q(k)sign(I(k))。将e(k)经环路滤波后反馈到NCO模块的相位控制字,调整本地载波频率。从而实现载波恢复。

4 IP core集成系统的验证与结论

在验证系统功能方面,文章中共采用了三种方式对设计的系统进行验证,分别是:Matlab下Simulink环境中的系统仿真、Quartus/Modelsim下的RTL仿真以及DSP开发板中的硬件仿真。测试流程如图3

图3.系统测试流程

其中基于PC仿真为FPGA开发板中验证打下基础。基于FPGA开发板验证分为自动流程和手动流程。

自动流程主要包括如下两个步骤:(1)Signal_Compiler完成HDL转换、综合、适配、下载。(2)嵌入式逻辑分析仪——SignalTap完成实时测试。

手动流程主要包括如下四个步骤:(1)Signal_Compiler完成HDL转换、综合、适配。(2)Quartus II完成适配、时序仿真。(3)芯片引脚锁定、配置下载、编程。(4)嵌入式逻辑分析仪——SignalTap完成实时测试。进行Matlab下Simulink环境中进行系统仿真时,通过波形直观的对输入数据和输出结果进行比较,验证系统的功能。同时我们还可以在系统中加入误码率统计模块对输入输出结果进行比较。

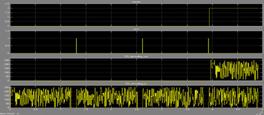

图4.是系统时序仿真图,其中第四路信号是信源产生的数据,通过解码后我们可以看到第三路信号在输入三个码字后输出译码结果。

图4. Matlab系统仿真时序图

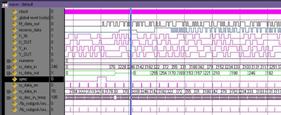

图5. Modelsim系统仿真时序图

使用Quartus II/Modelsim进行RTL仿真时,通过DSP_Builder中的Signal_Compiler模块将.mdl文件转化为.hdl文件,同时生成系统的测试文件和.tcl文件,只需要直接在Quartus II/Modelsim下调用.tcl即可执行RTL仿真。仿真结果如图5.

X_in、Y_in分别表示的I、Q两路信号。从图7可以看到,I、Q数据通过调制、加噪、解调后能够恢复出来,解调出来的I、Q两路数据送入解码器进行解码输出。

图6.FPGA中仿真波形图

在DSP开发板仿真验证时,通过Signal_Compiler模块对系统进行从.mdl文件向.hdl文件的转化、综合、适配,同时生成.stp文件;在Quartus II/Matlab下通过JTAG口将设计下载到Stratix II开发板中利用SignalTap完成实时测试,结果如图6.

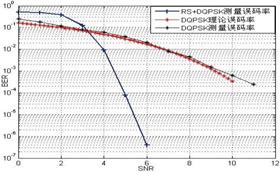

为了测试系统的误码特性,在FPGA开发板中引入噪声,使用误码分析仪进行了测量。图7.给出了未编码传输系统的理论误码曲线。在Pe=1e-3时,由于定时同步和载波同步等误差因素的影响,调制解调的实现损耗将近1dB,RS(204,188)编码增益为4~5dB,系统在不增加频带带宽的前提下,RS(204,188) 编码可以带来3~4dB的增益。

图7. RS(204,188)+DQPSK系统性能

5 总结

综上所述,基于IP系统集成的最大优点是:相对于纯软件方法:可以更好的解决速度、实时性和并行性问题,便于系统的开发。相对于纯硬件方法:有着灵活性和开发周期短的优势明显。测试方面:通过软件模拟和硬件仿真相结合的方法验证系统,有较强的综合性。

参考文献

[1] Altera,“Reed-Solomon Compiler User Guide”,Altera, Inc, 2004.7

[2] Altera,“NCO Compiler MegaCore Function User

Guide”,Altera, Inc, 2004 .9

[3] Altera,“FIR Compiler MegaCore Function User Guide”,Altera, Inc, 2004.12

[4] 任友,RS码编译码算法研究及其硬件实现, 成都电子科技大学, 2003.3

[5] 赵海潮,周荣花,沈业兵.基于FPGA的QPSK解调器的设计与实现[J].微计算机信息,2004

作 者 介 绍:王亮(1984-),男(汉族),籍贯湖北,清华大学硕士研究生,研究方向通信系统的可重配置的研究。

联系地址:(100084 清华大学电子工程系东主楼9区324)北京市清华园1号 100084

本文作者创新点:利用Altera公司的IP cores实现了RS+DQPSK的低中频调制解调系统,算法实现迅速;验证方法采用软件仿真与硬件仿真相结合,具较强的综合性。 |

|