上述分析结果表明,两条路径(reg4到reg1和reg4到reg2)都进行了Recovery和Removal检查。这个电路的Recovery时间检查(就象建立时间检测一样)差不多有9ns的slack,而Removal(就象保持时间检查一样)也有660ps的slack。两个检查都得到通过,意味着这个电路没有时序错误路径。

使用上述同步化异步复位的一个代价是它们很容易受到噪声和窄脉冲的干扰。同样地,如果可能最好对输入到FPGA的异步复位先进行滤波和去抖动。图16中的同步化异步复位原理图可以确保同步后的异步至少有一个时钟周期的长度,如果需要扩展复位长度到n个时钟周期,那么可以增加同步器中的寄存器个数到n+1个。请一定确保外部输入的异步复位reset_n连接到了所有同步器寄存器的CLRN端口,这样确保使得产生的同步化异步复位能够被异步地置位。

当有PLL涉及时,有些特殊情况需要考虑。比如我们来如图19所示的电路。需要同步的复位跟之前一样直接接到了同步器中寄存器的CLRN端口,而同步后的寄存器也同样接到了reg1和reg2的CLRN端口,同时也被接到PLL的areset端口。所有寄存器包括同步器中的寄存器的驱动时钟来自PLL的输出时钟。虽然看起来PLL使用了同步后的复位,实际上这是行不通的。当PLL处于复位状态时,PLL的c0是没有时钟输出的,因此同步器中的寄存器将无法清除复位(意思是复位无法得到释放)。结果是,这个电路将永远无法跳出复位。

图19:使用PLL时不正确实现同步化异步复位的原理图

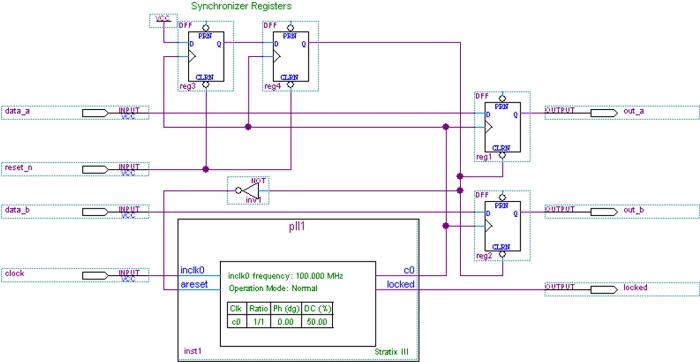

为了解决这个问题,PLL的复位应该使用FPGA原始输入的异步复位reset_n(如图20所示,这里进行了取反,这主要取决于复位是‘0’有效还是‘1’有效,这里不讨论),而不是同步后的复位。此外,使用PLL的Lock输出来作为同步器中寄存器的时钟使能,是个不错的做法。因为这将防止同步后的复位在PLL的输出时钟稳定之前提前释放。

图20:使用PLL时正确实现同步化异步复位的原理图

图21显示了图20所示是PLL正确实现同步化异步复位原理图的Verilog代码。

|