图21:使用PLL时正确实现同步化异步复位的Verilog代码

注意到上述代码中同步器的进程模块中多一个条件,即PLL的Locked信号,它作为同步器中的寄存器的同步时钟使能信号。同时注意下面例化的PLL以及两个个进程模块的时钟,这些都是当加入PLL时仅有的变化。

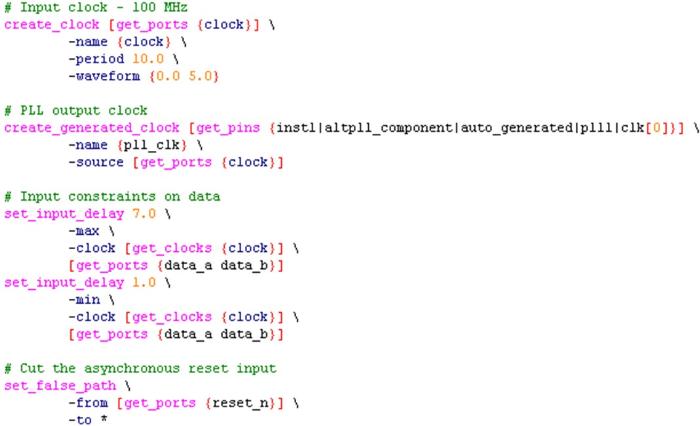

图22是需要给这个电路加入的SDC时序约束,基本和没有使用PLL相同,唯一的区别是需要使用create_generated_clock语句为PLL的输出时钟加约束(注意其实使用PLL后,可以直接使用语句derive_pll_clocks来简单地进行约束)。

图22:使用PLL时实现同步化异步复位的时序约束

最后,还有一个值得一提的例子。如前所述,设计中的不同时钟域的寄存器如果需要复位,应该首先将复位同步到当前的时钟域后再使用,也就是说每个时钟都需要有一套自己的复位同步器寄存器。而且,有的时候设计的某些部分可能需要比其它部分先从复位状态释放,所以这就需要一个复位释放顺序的安排。图23给出了这样一个例子,同步寄存器都通过类似菊花链方式串起来,我们看到最上面的同步器具有最高优先级从复位状态跳出来。图23所示的电路中,所有的复位都同时有效,但是rst_a_n具有从复位状态跳出的最高优先级,接着是rst_b_n具有中等优先级,rst_c_n是最后被释放的。当然,如果在不同复位之间需要更长的间隔时间,可以在同步器中添加任意个数寄存器来达到需要的间隔长度。

图23:不同时钟域同步化异步复位释放优先级安排

总结

本文介绍了不同复位的优缺点,比如同步复位,异步复位以及同步化的异步复位。同步复位需要一个时钟,所以窄复位脉冲将会被忽略,然后同时增加了系统的抗干扰能力。同步复位是百分之一百的同步电路,所以不存在亚稳态问题。只是同步复位会带来额外的资源消耗以及数据路径上的延迟,基于此我们说同步复位不是最佳复位选择。TimeQuest可以象分析其它数据路径那样分析同步复位。

异步复位通常立即起作用,也容易被实现,而且由于它们不象同步复位那样会给数据路径引入额外的延迟,所以复位速度很快。同时相比同步复位,异步复位消耗更少的逻辑资源。比较不幸的是,它们无法通过TimeQuest来进行时序分析(其它静态时序分析器也无法分析),而且如果处理不当还会给电路带来亚稳态问题。异步复位的最大弱点是它们无法确保所有的寄存器在同一个时钟沿处跳出复位状态。这在带反馈的同步设计中是会有问题的,比如状态机设计。

在将异步复位连接到寄存器的异步输入端口前给它加入一个同步器,这样就创造一个叫同步化了的异步复位。这种复位具有异步复位那样的立即将复位作用于电路好处,同时又提高电路速度,因为它们不会给数据路径带来额外的延迟。同时,这种复位象同步复位那样避免了亚稳态问题,而且保证所有的寄存器能够同时从复位状态跳出。不象异步复位,同步化了异步复位可以在TimeQuest里分析Recovery和Removal。正是由于这些原因,同步化了的异步复位是大部分FPGA设计中复位电路首先方法。 |