QPSK数字调制解调的FPGA实现,包括源程序(4)

|

- UID

- 1029342

- 性别

- 男

|

QPSK数字调制解调的FPGA实现,包括源程序(4)

6.QPSK解调的FPGA实现

经过调制后的数据具有50Mbit/s的信息速率,经过有符号数乘法模块,数据分别与相互正交的两正弦波相乘,相乘后的数据再经过FIR低通滤波器模块,滤除掉高频信号,经定时抽判模块生成码率为1.25Mbit/s的两列数据,最后经过并串变换模块合并为原先的2.5Mbit/s的符号速率。

系统框图

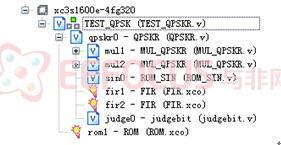

Verilog代码各个文件的逻辑关系入下图所示:

各个文件的逻辑关系

其中TEST_QPSK.V文件是测试文件,用来测试编写的Verilog代码是否正确,其中ROM文件中存放的经过MATLAB定点数仿真生成的QPSK调制数据,共有1K字节的数据量。测试文件通过没个时钟周期将ROM中存放的调制数据输出到编写的QPSKR文件中,实现解调测试。

QPSK.V文件是用到的解调文件的最上层文件,其对外端口如下:

module QPSKR(clk, en, DIN, dout, ready

);

input clk;

input en;

input [15:0]DIN;

output [1:0]dout;

output ready;

用两路正交的相干载波去解调,可以很容易地分离这两路正交的2PSK信号。相干解调后两路并行码元a和b,经过并/串变换后,成为串行数据输出。

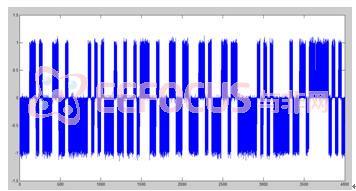

输入的数据与已经锁定的正交载波相乘后的输出结果如下图所示,图中只列出了一路信号的输出结果。

未滤波前的输出数据

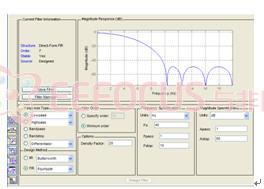

本文的一个设计重点在于滤波器的设计,使用MATLAB中滤波器协同设计单元,如下图所示,可以生成7阶滤波器,其系数为[0.0195568849377802 0.0684534436681266 0.136904053813160 0.188242810004127 0.188242810004127 0.136904053813160 0.0684534436681266 0.0195568849377802];

经过定点量化后得到0,23170,32767,23170,0,42366,32769,42366;将其写入到coe文件中作为滤波器的抽头系数。

FDATOOL工具输出结果

经过FIR低通滤波器后的输出结果如下图所示:

FIR滤波器输出的两路信号

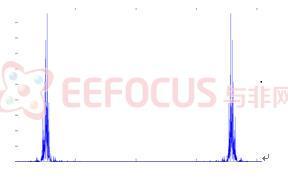

经过滤波器后的频谱如下所示,从图中可以看出带外信号已经衰减到很小值。

经过滤波器后的信号频谱

经过定时提取模块的抽判最后两路信号的输出结果如下,从图中我们可以看到dout输出的数据速率为1.25Mbit/s。  两路解调后的数据输出

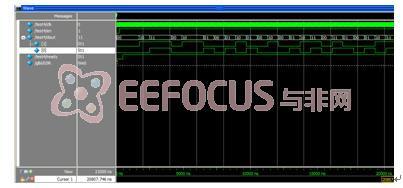

总上所述,当顶层模块检测到有有效数据到达时,en信号被置为高电平,此时信号输入到后解调模块,在输出端口,当ready信号有效时,在dout端口会有有效的数据输出。输出的数据如下所示:

|

|

|

|

|

|