超强宽幅图像处理系统可以这样设计,图像存储、压缩与回放统统实现

|

- UID

- 863084

|

超强宽幅图像处理系统可以这样设计,图像存储、压缩与回放统统实现

项目背景及可行性分析

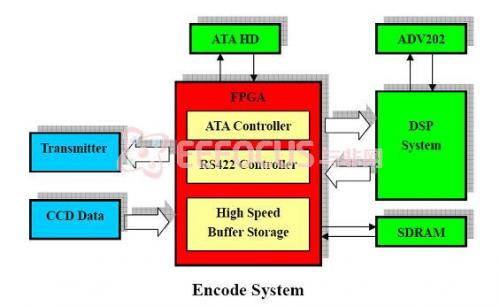

项目名称:宽幅图像存储、压缩与回放系统的研制与开发。本项目主要由两部分构成,包括编码板和解码板的开发与调试。编码板主要完成拍摄数据的无损存储和实时压缩,解码板主要完成压缩数据的实时解码和PC回放。目前,编码板与解码板可协同工作,完成图像存储、压缩与解压等基本功能,同时还能在PC上对解压图像进行回放。

本项目关键技术之一是高速大容量存储通道的设计,该设计摒弃了当前广泛采用的由操作系统控制硬盘进行存储的模式,转而采用FPGA在硬件底层上直接对硬盘进行控制,同时辅以SDRAM作为大容量高速数据缓存,极大地提高了硬盘的存储速率。本系统设计的另一亮点,即采用数据传输与数据压缩并行工作的方式,实现压缩码流传输时间的复用,极大提高了系统效率。在该方式下,数据发送任务由FPGA实现,缩短了DSP在数据发送任务上的时间开销,做到了图像压缩和数据传送的并行操作,对相机拍摄间隔时间的缩短起到了主要的作用。

在硬件设计上,本项目在设计之初便考虑了系统可靠性问题,对编码板和解码板采用镜像设计方法,使得系统调试更为简便,同时也增强了系统的可靠性。在软件设计上,以FIFO为基础的接口同步方案以及乒乓操作等数据缓存技术的使用,提高了软件在数据处理方面的可靠性。同时,基于FPGA的SDRAM、ATA外围存储设备控制在本小组所在实验室已是成熟技术。我们对系统连续进行200次拍照存储压缩试验,所测数据完全正确,这从一个侧面验证了系统的可靠性。

项目实施方案

数据存储、压缩和传输部分:

① 数据存储

宽幅图像数据量庞大,单幅图像约20MB,数据存储介质采用ATA接口标准的固态硬盘。现行ATA接口标准在PIO模式下的存储速率理论值为16.7MB/s,而CCD提供的数字接口速率约为25MHz,因此,系统采用SDRAM作为图像缓存。在硬件结构上,SDRAM和硬盘均由FPGA控制,该模块实现了一条完整的高速大容量存储通道,可在2秒内完成单幅原始图像数据的存储。

② 数据压缩

由于数据传输采用RS422接口,传输速率有限,不能直接将原始数据进行传输,因此需要进行图像压缩。系统采用专用JPEG2000压缩芯片ADV202,在DSP控制下读取硬盘数据,对图像进行分块压缩。

③ 数据传输

数据传输采用RS422接口,传输速率2Mb/s,在图像压缩比10:1的情况下,单幅图像压缩码流传输时间约8s。本系统采用数据传输与数据压缩并行工作的方式,实现压缩码流传输时间的复用,极大提高了系统效率。在该方式下,DSP操做ADV202对图像进行分块压缩,并将当前分割图像压缩数据快速传达SRAM,随后,FPGA操作SRAM从中读出数据,并按RS422接口标准发送。事实上,在FPGA进行数据传输的同时,DSP已经开始下一分割图像的压缩。这其实是资源与速度互换原则的体现。

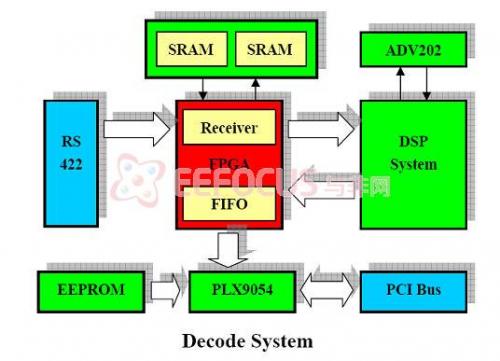

图像回放部分:

① 数据接收

数据接收主要由FPGA控制完成,有两大任务,一是将有效数据从传输帧结构中提取出来,二是将压缩图像数据和系统参数数据分离。实现时,FPGA控制两片SRAM乒乓操作实现压缩数据的接收,其中每片SRAM负责存放一幅完整的图像压缩数据,保证输入数据流和输出数据流连续不断,使得数据接收更加高效、稳定。

② 数据解压

数据解压部分整体上同数据压缩部分成镜像关系,采用专用的JPEG2000压缩芯片ADV202,在DSP的控制下读取存储在SRAM中的压缩图像数据,对图像进行分块解压。

③ 数据回放

数据回放部分主要通过PCI接口将图像解压数据和系统参数传至PC进行显示。PCI接口由PCI9054实现,在PCI局部总线端采用Scatter/Gather DMA模式接收数据。PCI DMA传输时序和DSP并不兼容,因此,同步数据接口采用FIFO存取方法,通过FPGA实现从DSP到PCI数据接收端口的时序转化。

以FPGA为枢纽的硬件平台开发需要FPGA具有丰富的IO引脚和足够的逻辑资源。本项目在Spartan3系列的FPGA下进行开发,开发软件包括ISE8.2,ChipScope以及ModelSim等。

主要开发模块包括:高速缓存系统模块、硬盘控制模块、RS422发送控制模块、数据接收模块、PCI接口模块等。模块开发主要由仿真和实测两部分构成。

系统最终在10秒内完成一幅宽幅图像的存储、压缩、传输和回放功能。 |

|

|

|

|

|