|

- UID

- 1029342

- 性别

- 男

|

求取MFcc参数的大致过程如下:

(l)预加重Pre一emphasis,加强语音中的高频部分。

(2)加窗Windowing,使语音平滑过渡,保持自相关性。

(3)对加汉明窗后的语音帧作快速傅立叶变换 (FastFourierTransformation,FFT),将时域信号转化为频域 (FrequencyDomain)信号。

(4)从FFT输出的数据取模的平方后,得到其离散功率谱,并通过一组三角带通滤波器 (TriangularFihers)。

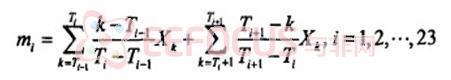

其中,Xk为功率谱上第k个点的值,mi为第i个滤波器的输出,Ti为第i个滤波器的中心频率。

(5)将三角滤波器组的输出取自然对数,用离散余弦变换 (DisereteCosine升即sformation,DCT)将滤波器输出变换到倒谱域,即可得到MFCC。

其中,P为MFCC参数的阶数。Mk为MFCC参数。

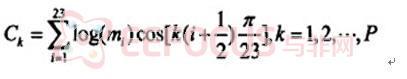

MFCC特征提取的硬件设计流程如图:

由于在端点检测的时候已经进行了预加重和加窗处理,所以直接从FFT部分开始计算,FFT模块的输入除了加窗后的语音还有一帧语音的开始和结束(就是端点检测模块的输出win_data、sop和eop)。因为语音数据都是实数,所以本文在FFT运算上提出了一点改进,可以加速FFT运算速度。FIFO缓冲的读写速度是不一样的。如果前一帧的MFCC参数计算已经完成,并且FIFO中的数据个数大于128(FFT变换后取前面128个值),帧RAM就读128个数据(即一帧)到帧RAM中,并发出信号表示新的一帧计算开始,在该帧没有计算完成之前是不能有新的数据进入帧RAM的。为了加快MFCC参数计算速度,本文将三角滤波器组、对数运算和DCT三个串行的模块,设计成三级流水处理。

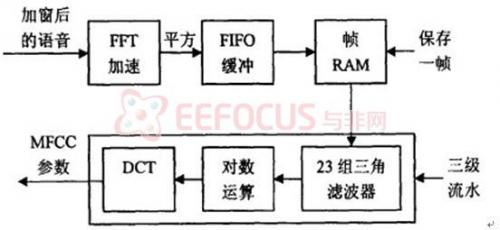

本实验中FFT的设计是在ISE10.1软件平台下完成的,在软件平台上,选用V6的板,直接条件FFT的IP核,对I/O数据流结构选项包括:流、缓冲突发和突发(Burst)进行处理,对参数进行设定

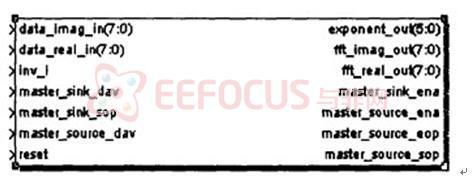

dsta_imag_in:输入数据的虚部。

dsta_real_in:输入数据的实部。

Inv_i:为1表示做IF可变换,为O做FFr变换。

master_sink_dsv:置位表示数据源准备好。

master_sink_sop:置位表示输入模块的开始。必须和输入模块的第一个样点同步,并维

持一个时钟周期。

master_source_dav:置位表示设备接受器可以接受输出数据模块。

reset:置位表示同步复位。

exponent_out:表示FFr输出数据的指数。

fft_imag_out:输出数据的虚部。

fft_real_out:输出数据的实部。

master_sink_ena:FFT核函数准备好,可以将输入模块写入其输入缓冲。

master_source:FFT输出数据准备好,可以送到数据接受器。

master_source_eop:输出模块数据包的终点。

master_source_sop:输出模块数据包的起点。 |

|