|

- UID

- 1023229

- 来自

- 中国

|

2.3 外围电路模块

2.3.1 D/A转换

在D/A选择上,我们用的是美国半导体公司的 DAC0832,它具有8位并行、中速(建立时间1 us)、电流型、价格低廉等特点。它有单缓冲工作方式、双缓冲工作方式两种工作方式。单缓冲工作方式时,一个寄存器工作于直通状态,一个工作于受控锁存器状态。在不要求多相D/A同时输出时,可以采用单缓冲方式,此时只需一次写操作,就开始转换,可以提高D/A的数据吞吐量。双缓冲工作方式时,两个寄存器均工作于受控锁存器状态。当要求多个模拟量同时输出时,可采用双重缓冲方式。

它的技术参数为:建立时间1 us;8位并行;低功率损耗20 mW;支持电压:5 V~15 V。

2.3.2 运算放大

在D/A转换之后,我们得到的是电流信号,而需要输入示波器的为电压信号,因此运用运算放大器来进行转换,同时将运放设计为可调形式,通过调节它便可以调节输出电压的大小,达到控制显示幅值的目的。本设计采用LM741系列运放,其技术指标加下:

3 系统软件设计

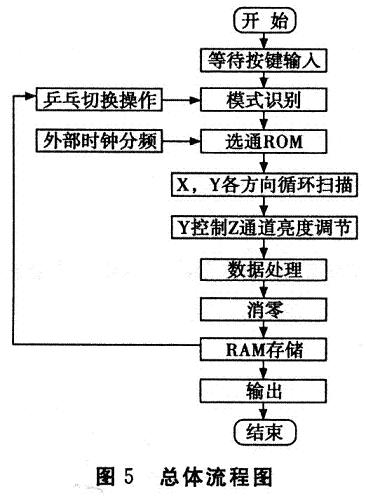

基于VHDL语言的功能与灵活性,非依赖性和可移植性种种优势,本设计在FPGA编程上采用了VHDL语言实现。总体设计思路:采用50 MHz外部时钟控制对FPGA内部进行分频控制,在分频模块的作用下得到设计所需要的时钟信号。通过按键选通在ROM内部选择要显示的模块部分,进行X、 Y方向扫描,得到初步的数据,同时外加Z方向扫描来控制所显图形的亮度。通过将所有的“1”存储在一个ROM中作为缓存,达到消除零点的目的。将ROM中的数据转移到RAM中,通过乒乓交换操作来进行模式转换,最后通过外围电路输入示波器,实现显示。总体流程图:

4 结语

本文是基于FPGA的数字示波器图文显示系统的硬件/软件的设计思路和设计方案。此系统设计完成后,测试表明系统可以将相应的图形文字显示出来,显示的图形和文字与预期的基本一致。该设计满足了系统的需要,更重要的是具有很强的灵活性和可控性,同时使显示更加高速度快捷,具有非常广阔的应用前景。 |

|