基于MEMS强链和FPGA的USB移动硬盘数据加解密系统2

|

- UID

- 1023229

- 来自

- 中国

|

基于MEMS强链和FPGA的USB移动硬盘数据加解密系统2

不失一般性,我们讨论下执行DMA 读命令的全过程。首先,在PIO 状态下将DMA 读命 令的代码0xC8(或0x25)写入硬盘的命令寄存器。此后状态机进入DMA 读状态,总线切换给 DMA 读数据接收模块和DMA 读数据发送模块。DMA 读数据接收模块与硬盘进行握手确认, 启动UDMA 读传输,此后每当硬盘DMA strobe 信号(DMA 同步信号)发生跳变,就对16 位 硬盘数据总线进行采样,并更新CRC 接收校验;每采样8 次则整合成一个128 位并行数据,提 供给AES 解密模块,该模块取走这128 位数据开始新一轮AES 解密迭代运算,同时输出前一 轮处理完的128 位解密数据,并拆分为8 个16 位并行数据,陆续存入一个16 位宽的FIFO。与 此同时,DMA 读数据发送模块查询到FIFO 中出现了数据,就开始不断的从中读取,并放在16 位数据总线上提供给USB 控制器,每放一次数据,便翻转一次DMA strobe 电平使得USB 控制 器的GPIF 接口能够同步接收数据,同时更新CRC 发送校验。

当硬盘把所有指定数量的加密数据都发送给FPGA 后会收到FPGA 的CRC 接收校验反馈, 若与硬盘内部的CRC 校验一致,则硬盘认为这次DMA 读命令被正确执行。

当 FPGA 把所有处理完的解密数据都发送给USB 控制器后也会收到USB 控制器的CRC 校 验反馈,若与FPGA 内部的CRC 发送校验一致,则可以认为一次完整的含解密的DMA 读命令 被正确执行。

图 3 中的全局控制状态机负责整个系统的控制和协调,它实时的监测PIO 写入命令,并在恰当的时机把IDE 总线控制权切换给加密流水线或解密流水线。当加解密流水线执行完一次 DMA 传输命令后,总线控制权会重新交还给全局控制状态机。

5. AES 加密模块的实现

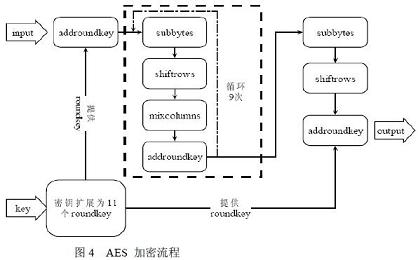

AES 的设计原理可参考文献[1],下面只简单介绍算法过程。AES 是一个迭代的分组密码, 每一轮迭代称为一个轮变换,包括一个混合和三个代换:

(1)字节代换(SubBytes):利用S 盒对状态的每一个字节进行非线性变换。

(2)行移位(ShiftRow):对状态的每一行,按不同的位移量进行行移位。

(3)列混合(MixColumn):对状态中的每一列并行应用列混合,在最后一轮省略该步。

(4)扩展密钥加(AddRoundKey):与扩展密钥异或。 加密算法的流程如图4 所示。

相应的,解密算法使用逆序的扩展密钥,轮变换分别为InvSubByte,InvShiftRow, InvMixColumn,数据流程稍有不同。

我们设计的AES 加密运算模块以128 位为一个分组,完成一个分组的运算需要11 个时钟 周期。第1 个时钟周期,密钥扩展模块输出第1 个扩展密码,也就是初始密码本身;同时初始 变换模块用这个扩展密码对128 位明文作AddRoundKey 操作。

第2 个到第11 个时钟周期,密 钥扩展模块依次生成10 个扩展密码,同时,轮变换模块利用这些扩展密码对输入密文作10 个 轮次的轮变换,其中最后一轮缺少列混合操作,然后输出最终的密文,结束一个分组的运算。

6. 数据吞吐率分析

Ultra DMA 在模式2 下的数据传输率为33.33MB/s。由于FPGA 全局时钟频率为100MHz, 所以加解密一个128 位分组需要110ns。加上数据的输入和输出阶段各占用一个时钟周期,总共 需要130ns。所以加解密模块的数据处理速率约为61.54MB/s,完全能够达到实时处理的要求。

7. 结束语

本文提出了一种安全高效的USB 移动硬盘数据加解密系统。其中,MEMS 强链的应用开辟 了系统物理认证的新方向;Ultra DMA 协议接口的FPGA 实现大大提高了硬盘读写的吞吐率,同时AES 加解模块的处理速率又能完全满足Ultra DMA 传输带宽,两者的有机协作使得一种高 效的硬件加解密流水线得以实现。 |

|

|

|

|

|