(5)参考TBUF的设置。设计中通过约束参考TBUF的位置来决定整个总线宏的位置,若用户没有设置参考TBUF,则FPGA Editor工具会将用户添加的第一个TBUF默认为参考TBUF。

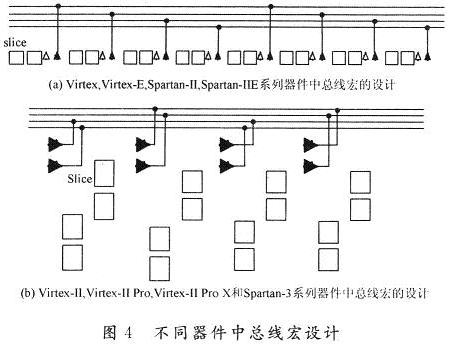

至此,整个总线宏的设计完成,如图4所示。

3 总线宏的验证

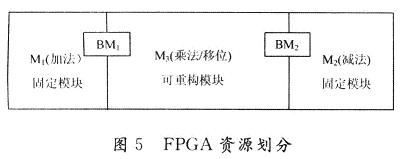

为了验证上述总线宏设计方法的正确与否,这里设计了一个功能简单的FPGA动态局部可重构实验。电路重构前实现的功能为:(A+B)*(C-D),重构后实现的功能为:(A+B)》(C-D)。根据电路功能将电路划分为3个模块。其中,加法(A+B)、减法(C-D)为固定模块M1,M2;乘法/移位(*/》)为可重构模块M3。M1与M3,M2与M3之间分别用总线宏BM1和。BM2实现通信,如图5所示。

该实验采用的软件开发平台:Xilinx ISE6.2i;硬件开发平台:可重构硬件平台——XCV800验证板。

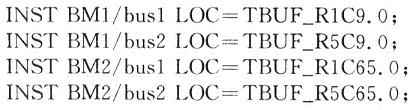

每一个总线宏只能传递4位的信号。当可重构模块间需要多于4位的数据通信时,可以通过多个总线宏的拼接实现。这种拼接只是简单地将多个宏拼接为一个文件,而不是将多个宏拼接为一个宏,所以在使用约束语句,约束总线宏的位置时,仍然必须单独约束每个宏,而不是直接约束一个文件。例如该实验中模块M1与模块M3之间的数据通信是8位,则需要2(8/4)个总线宏来实现模块M1与M3间的通信,M2与M3之间也一样:

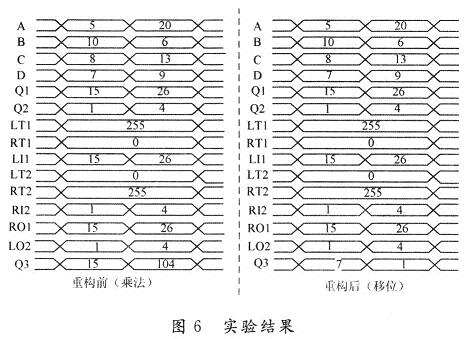

按照FPGA动态可重构软件设计流程生成局部动态可重构.bit文件;通过JTAG电缆下载到可重构硬件平台——XCV800验证板进行调试验证;通过逻辑分析仪观察结果,如图6所示。

A,B的和Q1作为总线宏BM1的数据输入LI1;C,D的差Q2作为总线宏BM2的数据输入RI2;BM1和BM2的方向控制端LT1,RT2为高(255),RT1,LT2为低(O);数据输入端RI1,LI2悬空,R01,L02分别为总线宏的输出;Q3为可重构模块M3的输出。由实验结果可知,总线宏的设计是正确的。

4 结 语

目前,Xilinx公司提倡使用最新的EAPR(Early Access Partial Reconfiguration)方法实现FPGA动态局部可重构技术。该方法中用于可重构模块与其他模块之间通信的总线宏是基于Slice的,但这个方法只适用于Virtex-Ⅱ,Virtex-ⅡPro,Virtex-IV和Virtex-V等器件,对于Virtex,SpartanⅡ,SpartanⅢ等器件,只能使用基于TBUF的总线宏实现动态可重构技术,因此该文对基于TBUF的总线宏研究是有意义的。 |