1 引言

随着集成电路工艺技术的不断发展和集成度的提高,嵌入式系统由板级向芯片级过渡,形成一种新的设计方法一片上系统(System on Chip,简称SoC)。SoC从整个系统的角度出发,把处理机制、模型算法、芯片结构、各层次电路,直至器件的实际电路紧密连接起来,在单个(少数几个)芯片上实现整个系统的功能。同时随着现场可编程逻辑阵列(FPGA)技术的日益成熟,将PLD与嵌入式处理器IP软核相结合,形成基于可编程片上系统(System on Programmable Chip,简称 SoPC)的SoC解决方案,使得更加灵活的SOPC成为现代嵌入式系统设计的发展趋势。SoPC是Altera公司提出的一种灵活、高效的SoC解决方案。它将处理器、存储器、I/O口、LVDS、CDR等系统设计需要的功能模块集成到一个可编程器件上,构成一种特殊的可编程片上嵌入式系统。一方面,它是可编程片上系统,即由单个芯片完成整个系统的主要功能,并具备软硬件系统可编程的能力;另一方面,它内嵌处理器IP核,具有灵活的设计方式,用户可根据需要随意配置、构建、裁剪处理器IP核。目前最具有代表性的IP软核嵌入式处理器是Altera的NiosII软核。NiosII嵌入式CPU是一种专门为SoPC设计应用而优化的CPU软核。

在基于NiosII的SoPC嵌入式系统中,几乎所有的应用设计都需要使用Flash来保存在NiosII中运行的程序代码、非易失性数据和FPGA的配置数据。因此Flash编程便成为在调试完SoPC系统后的重要工作。要对Flash编程,首先要保证在SoPC Builder中Target选项区域的Board下拉列表框中选择用户使用的目标板F1ash编程设计。基于实际设计需求,详细介绍SoPC目标板Flash编程设计的创建,并以一个最小SoPC系统为例,说明目标板Flash编程设计的应用及Flash编程。

2 Flash Programmer简介

NiosII IDE提供了Flash Programmer工具来对目标板上遵循通用Flash接口(Common Flash InteRFace,简称CFI),规范的Flash及EPCS配置器件进行编程。IDE的FlashProgrammer通过使用Altera的下载电缆能够方便地对目标板上连接在FPGA上的Flash及串行配置器件EPCS进行编程。

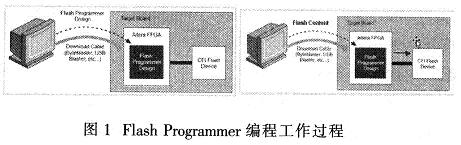

2.1 Flash Programmer编程工作过程

NiosII的IDE Flash Programmer采用两步骤将数据写入Flash中。第一步,用一个Altera提供的特殊Flash编程设计(Flash Programmer Design)对FPGA进行配置;第二步,IDEFlash Programmer将要编程到Flash中的文件内容传送到在FPGA上运行的Flash编程设计,然后Flash编程设计将接收到的数据编写到Flash中。其编程工作过程如图1所示。

2.2 Flash编程设计

Flash编程设计实际就是一个由SoPC Builder系统生成的最小FPGA设计。Flash编程设计是IDE Flash Programmer的关键组成部分。不同的目标板往往使用不同的Flash器件,并且Flash与FPGA的引脚连接以及FPGA的型号也不相同。因此,每个Flash编程设计都是与具体的目标板相联系的,不能用于其他的目标板。如果使用自己的目标板,那么设计者必须创建该目标板的Flash编程设计。Altem公司的Nios开发板都提供了相应的Flash编程设计,可以在NiosII开发套件安装目录的、ipnios2_ip文件夹中找到。

2.3 Flash编程设计信息

目标板Flash编程设计描述了系统与目标板之间的关系。目标板Flash编程设计对Flash编程必不可少,它提供了Flash Programmer对Flash编程所需的全部信息。一个目标板Flash编程设计是一组SOPC Builder文件,其中必须指明FPGA与Flash的连接关系。一个目标板Flash编程设计包含下列信息:①每一个连接到电路板FPGA上的F1ash的参考元件标号,如U7,U7Flash,U3EPCS等;②Flash器件在F1ash编程设计中的基地址;③用于配置目标板上FPGA的Flash编程设计的SOF文件。

参考元件标号用于区分设计中不同的Flash器件。目标板上的Flash器件在设计时的命名和基地址可能不同,但参考元件标号总是相同的。

3 目标板Flash编程设计的创建

用户自制目标板,而在Target选项区中的Board下拉列表框中没有相应的目标板Flash编程设计,用户就必须自己创建目标板Flash编程设计。

3.1目标板Flash编程设计文件创建

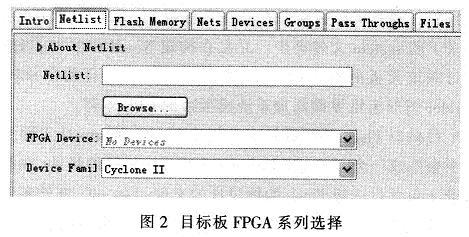

下面以QuaausII 7.0为例,详细说明目标板Flash编程设计的创建。目标板Flash编程设计在SoPC Builder中实现。在QuaausII中新建一个工程,在[Tools]菜单中选择[SoPC Builder],打开Ahera SOPC Builder图形编辑界面环境。在SoPC Builder图形编辑界面中,在[File]菜单中选择[New Board Description],打开Board Description Editor对话框,在此对话框中选择NetList页面,在Device Familv栏中正确选择目标板的FPGA系列,这里以Cyclone II为例,如图2所示。

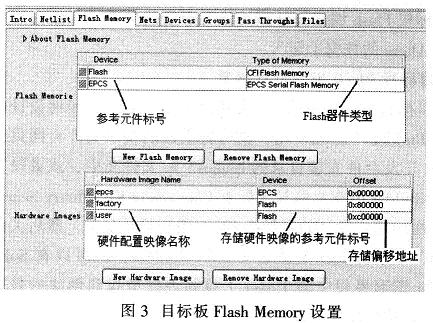

选择Flash Memory页面,单击New Flash Memory按钮添加目标板的Flash器件,并输入正确的连接到目标板FPGA的参考元件标号和Flash器件类型。参考元件标号可命名为用户的任意字符串,如U7,EPCS,Flash等,但不能命名成U7(CFIFlash),U3(EPCS)等形式。再单击此页面的New HardwareImage按钮,指定FPGA硬件配置程序的存储位置,一般选择EPCS器件。如果设置为Flash器件,需要有相应的外部控制器、单片机或CPLD配合使用。设置如图3所示。

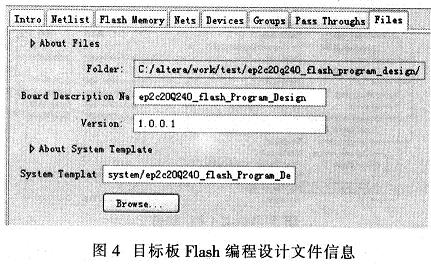

FPGA硬件配置可放在NOR Flash中,也可放在EPCS中。在Hardware Image Name栏下输入硬件配置映像的名称,如epcs,user,factory等。对于每一个Hardware Image Name,都要选择一个用来存储的Flash。如果用户设计中,即采用EPCS,又采用NOR Flash对FPGA的配置数据进行存储,则可在Hardware Image Name栏下输入两个硬件配置映像名,如user,factory,然后分别指定为前面的参考元件标号;对于offset栏的设置,如果对应的Device栏为Flash器件,则可以指定硬件映像在Flash中的编程偏移地址;如果对应的Device栏为EPCS器件,则不能在offset栏中指定偏移地址。最后选择Files页面,输入Board Description Name,Version和System Template,单击Finish按钮完成目标板Flash编程设计的创建,如图4所示。

System Template栏可通过Brows按钮选择设置的系统模板*.ptf(或者直接输入),也可不设置系统模板。如果设置系统模版,则系统模板需要存储在目标板Flash编程设计文件目录下的system文件夹中。并且在构建NiosII CPU时,当选择带系统模板的目标板Flash编程设计时,会自动在SoPCBuilder图形编辑界面添加系统模板带的CPU组件。

目标板Flash编程设计成功创建后,在QuartusII工程目录下会生成一个与Board Description Name相同的目录。在此目录下包含目标板Flash编程设计的文件class.ptf。文件夹下还包含两个子文件夹,一个是system,设计者指定的系统模版便存放在此;另一个是netlist,存储设计者提供的PCB网表文件,格式为wirelist。如果设计者不需要这两个文件,则为空文件夹。

对于Board Description Editor对话框中其他页面的选项,与目标板Flash编程设计描述没有必要的关系。详细内容请参见Altera的数据手册。

3.2 目标板Flash编程设计设置

目标板Flash编程设计成功创建后,为了在任何设计的SoPC Builder中都能使用,则可将生成的整个文件夹拷贝到NiosII开发套件安装目录的ipnios2_ip文件夹中,或者设置SoPC Builder的搜索路径,配置Component/Kit Library SearchPath,增加用户设计的目标板Flash编程设计目录。然后关闭Ahera SoPC Builder重新启动SoPC Builder,就可以在SoPCBuilder图形界面中的Target下拉列表框中找到创建的目标板Flash编程设计。

4 目标板Flash编程设计的应用

以一个最小SoPC系统流水灯为例,说明目标板Flash编程设计在实际Flash编程中的应用。

4.1 NiosII CPU生成

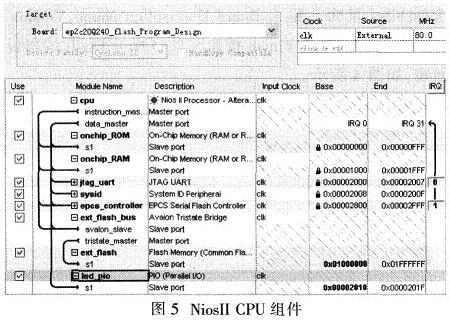

在Altera SoPC Builder图形界面中,首先在Target选项区中Board下拉列表框中选择刚创建的目标板Flash编程设计,并指定NiosII系统的时钟。然后添加系统所需的外设元件,设置各外设元件的参数。分配Base Address和IRQ。添加完组件后如图5所示。

添加完组件后,在Nios II More“cpu”Settings中设置复位地址和异常地址。如果Nios程序下载到Flash中,则复位地址设为ext_flash;如果下载到EPCS中,则复位地址设为epcs_controller。最后在System Generation中点击Generation按钮生成NiosII CPU。

4.2 构建最小SOPC系统

在QuartusII中构建最小SoPC系统。此SoPC系统由NiosII CPU模块、PLL模块和系统复位模块组成。在系统的顶层模块中分别添加SoPC Builder生成的NiosII CPU,PLL模块及系统复位模块构成最小的SoPC系统。由于目标板上时钟是50 MHz,而构建NiosII CPU时钟设为80 MHz,故需通过Mega Wizard Plug-In Manager生成PLL模块,将系统时钟提高到80 MHz。添加完模块后,再添加输入/输出端口,并连接引脚与端口,命名端口名(建议端口命名与实际电路中的网络标号相同)。然后分配引脚,并设置相关参数。编译工程生成FPGA的配置文件*.sof,并利用QuartusII的Programmer下载到FPGA或EPCS中。

4.3 Nios程序生成及Flash编程

启动NiosII IDE,建立和编译一个简单的LED流水灯的Nios应用程序。在Nios应用程序调试正确后,单击菜单[Tools]下的[Flash Programmer],弹出Flash Programmer编程界面。选中Flash Programmer,单击New按钮创建一个FlashProgrammer配置。在Flash Programmer界面中选择Main选项卡,设置Flash Programmer相关参数。

如果选中Program software project into flash memory project项,表示将工程的*.elf文件写入Flash(EPCS或CFI Flash)存储器中。将*.elf文件写入Flash的过程时,如果工程没有编译连接,会自动进行工程的编译连接。对于*.elf文件的编程,Flash Programmer窗口中并没有存储器和偏移地址的设置,存储器和偏移地址由是SOPC Builder中Reset Address指向的存储器和设置的偏移地址决定。如果将ResetAddress指向CFI F1ash.偏移地址从0x0HD开始,那么FlashProgrammer就会从CFI Flash的基地址+0x00开始烧写数据;如果将Reset Address指向epcs_controller,偏移地址从Ox00开始,那么Flash Programmer就会从EPCS的基地址+配置数据空间+Ox00开始烧写数据。

如果选中Program FPGA configuration data into hardware-image region of flash memory,可将FPGA配置数据写入Flash(EPCS或CFI Flash)。选择作为硬件系统的FPGA配置文件*.sof,指定配置文件的硬件配置映像名及存储的偏移地址。如果在制作目标板Flash编程设计时,指定可将配置文件编程到CFIFlash,并指定多个偏移地址,此项就可选择编程地址,从而将配置文件编程到用户指定的存储器地址空间。对于将配置文件编程到EPCS,偏移地址只能从Ox00开始。如果选择Program file into a flash memory选项,能将指定的二进制文件写入指定的Flash(EPCS或CFI Flash)存储地址空间。

在Flash Programmer界面中选择Target Connection选项卡,设置当前所用的下载电缆及JTAG器件。然后单击Program F1ash对Flash进行编程(EPCS或CFIFlash)。如果看到图6所示的提示消息,则Flash编程已经成功,说明目标板Flash编程设计创建成功。

5 结语

实现SoPC目标板Flash编程设计的创建,并通过一个最小SoPC系统说明目标板Flash编程设计在Flash编程中的应用及Flash编程的方法。通过实验验证了目标板Flash编程设计创建方法的正确性,并能对Flash编程。 (发布者:chiying) |