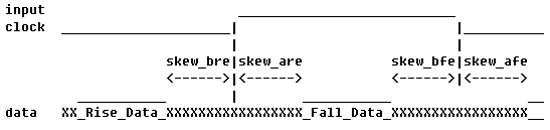

DDR 源同步边沿对齐输入接口

已知条件如下:

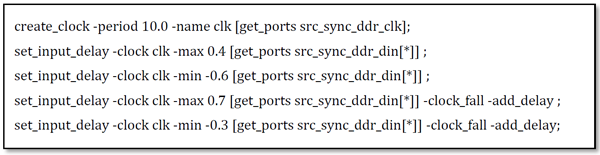

时钟信号 src_sync_ddr_clk 的频率: 100 MHz 数据总线: src_sync_ddr_din[3:0] 上升沿之前的数据 skew (skew_bre ) : 0.6 ns 上升沿之后的数据 skew (skew_are ) : 0.4 ns 下降沿之前的数据 skew (skew_bfe ) : 0.3 ns 下降沿之后的数据 skew (skew_afe ) : 0.7 ns可以这样计算输入接口约束:因为已知条件是数据相对于时钟上升沿和下降沿的skew,所以可以分别独立计算;上升沿的 -max 是上升沿之后的数据 skew (skew_are ),对应的-min 就应该是负的上升沿之前的数据 skew (skew_bre );下降沿的 -max 是下降沿之后的数据 skew (skew_afe ),对应的-min 就应该是负的下降沿之前的数据 skew (skew_bfe )。

所以最终写入 XDC 的 Input 约束应该如下所示:

出现负值并不代表延时真的为负,而是跟数据相对于时钟沿的方向有关。请一定牢记 set_input_delay 中 -max/-min 的定义,即时钟采样沿到达之后最大与最小的数据有效窗口(set_output_delay 中 -max/-min 的定义与之正好相反,详见后续章节举例说明)。

在这个例子中,数据是边沿对齐,只要有 jitter 跟 skew 的存在,最差情况下,数据有效窗口在到达时钟采样沿之前就已经结束,所以会有负数出现在-min 之后。因此,在实际应用中,FPGA 用作输入的边沿对齐 DDR 源同步接口的情况下,真正用来采样数据的时钟会经过一个MMCM/PLL 做一定的相移,从而把边沿对齐变成中心对齐。

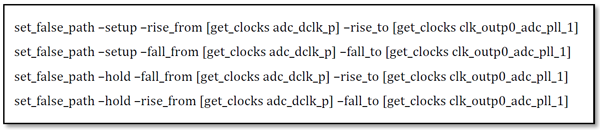

另外,在经过 MMCM/PLL 相移后的采样时钟跟同步接口输入的时钟之间需要做set_false_path 的约束(如下述例子)而把那些伪路径从时序报告中剔除,这里不再详述。

虚拟时钟

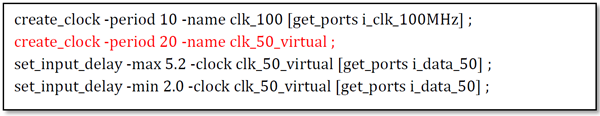

在 FPGA 做系统同步输入接口的情况下,很多时候上游器件送入的数据并不是跟某个 FPGA 中已经存在的真实的时钟相关,而是来自于一个不同的时钟,这时就要用到虚拟时钟(Virtual Clock)。

举例来说,上游器件用一个 100MHz 的时钟送出数据到 FPGA,实际上这个数据每两个时钟周期才变化一次,所以可以用 50MHz 的时钟来采样。FPGA 有个 100MHz 的输入时钟,经过 MMCM 产生一个 50MHz 的衍生时钟,并用其来采样上游器件送来的同步数据。

当然,系统级的设计上,必须有一定的机制来保证上游器件中的发送时钟和 FPGA 中的接收时钟的时钟沿对齐。

此时,我们可以借助虚拟时钟的帮助来完成相应的 Input 接口约束。

篇幅所限,对 XDC 中 I/O 约束的设计思路、分析方法以及如何具体设置 Input 接口约束的讨论就到这里,下一篇我们接着分析如何设置 Output 接口约束,看看 Vivado 中有什么方式可以帮助用户准确便捷地定义接口时序约束。 |