(9)向工程添加FIFO模块文件。

生成FIFO模块的文件后,在工程的目录下生成了选择的文件。要在工程中调用这些模块,首先要将这些文件添加到工程中来。

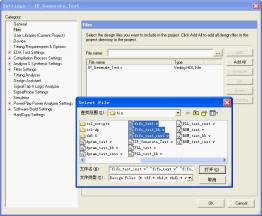

打开“Project”菜单,选择其中的“Add/Remove Files in Project…”选项,如图9.17所示,打开工程添加/删除文件对话框。

在打开的对话框中,选择向工程添加3个文件,如图9.18所示。

图9.18添加FIFO模块文件

图 9.19工程浏览器

添加成功后,在工程浏览器中,可以看到器件设计文件中已经包含了这3个文件,如图9.19所示。

(10)FIFO模块实例化。

将模块文件加入工程后,设计者就可以调用这个片上FIFO,并实例化了。

首先我们看一下Quartus II是如何构建这个FIFO的。打开fifo_test.v文件,这是FIFO模块的构造设计文件。该构造设计文件主要可以分为下面4个部分。

第一部分是端口声明和说明,这部分是根据用户自定义选择的控制信号及深度、宽度等参数决定的,代码如下:

module fifo_test (

data, //数据输入

wrreq, //写请求

rdreq, //读请求

clock, //时钟

aclr, //异步清零

q, //数据输出

full, //满信号

empty, //空信号

usedw); //字节使用信号

input [31:0]data; //输入数据宽度

input wrreq;

input rdreq;

input clock;

input aclr;

output [31:0]q; //输出数据宽度

output full;

output empty;

output [10:0]usedw; //自动计算出的字节使用控制信号宽度

第二部分是FIFO端口信号与Altera宏模块之间的连线声明,其中只有输出信号需要声明,而输入信号可以直接调用,代码如下:

wire [10:0] sub_wire0; //usedw输出类型声明

wiresub_wire1; //空信号输出类型声明

wire [31:0] sub_wire2; //数据输出类型声明

wiresub_wire3; //满信号输出类型声明

wire [10:0] usedw = sub_wire0[10:0]; //usedw连线

wireempty = sub_wire1; //空信号连线

wire [31:0] q = sub_wire2[31:0]; //数据输出连线

wirefull = sub_wire3; //满信号连线

第三部分是实例化FIFO所调用的宏模块,这里调用的是scfifo模块,代码如下:

scfifo scfifo_component ( //scfifo模块实例化

.rdreq (rdreq), //读请求

.aclr (aclr), //异步清零

.clock (clock), //时钟

.wrreq (wrreq), //写请求

.data (data), //输入数据

.usedw (sub_wire0), //字节使用信号

.empty (sub_wire1), //空信号

.q (sub_wire2), //数据输出

.full (sub_wire3) //满信号

.almost_empty (), //几乎空信号

.almost_full (), //几乎满信号

.sclr () //清零信号

.);

第四部分是参数设置,这里设置的是scfifo模块的参数,包括宽度、深度以及之前生成步骤中设置的那些参数,代码如下:

defparam

scfifo_component.lpm_width = 32, //宽度为32位

scfifo_component.lpm_numwords = 2048, //深度为2048字节

scfifo_component.intended_device_family = "Cyclone",//器件族为Cyclone

scfifo_component.lpm_type = "scfifo", //调用lpm为scfifo

scfifo_component.lpm_showahead = "OFF", //关闭showahead模式

scfifo_component.overflow_checking = "ON", //打开溢出校验

scfifo_component.underflow_checking = "ON", //打开读空校验

scfifo_component.add_ram_output_register = "ON"; //使用输出寄存器

在生成的3个FIFO模块文件中,还包含一个fifo_test_bb.v文件,这个文件包含的是fifo_test.v文件的第一部分内容,也就是说这个文件是FIFO模块的端口声明模块。 |